El mercado de los PCs con IA y del edge AI continúa acelerándose, presionando a los SoCs avanzados para ofrecer más ancho de banda, menor consumo y mejor integridad de señal. En este contexto, Cadence ha anunciado un hito relevante: la disponibilidad de su solución eUSB2V2 fabricada en 3 nm, diseñada para responder a las exigencias de conectividad de PCs con IA, portátiles y sistemas de imagen de nueva generación.

Según proyecciones del sector, los AI PCs representarán una parte cada vez mayor del mercado global en los próximos años, mientras que el edge AI se multiplica gracias a algoritmos más eficientes, silicio de IA más potente y la expansión del IoT. Todo ello incrementa la demanda de interfaces rápidas que mantengan bajo voltaje de E/S y reduzcan EMI/RFI, especialmente en nodos avanzados de 5 nm y por debajo.

eUSB2V2 a 3 nm: más velocidad con menor consumo

La propuesta de Cadence se apoya en el estándar eUSB2V2, ofreciendo hasta 4,8 Gbit/s a bajo voltaje, con tasas de datos simétricas y asimétricas y una integridad de señal optimizada para SoCs modernos. El objetivo es claro: sostener cargas de trabajo de IA, cámaras de alta resolución y altas tasas de fotogramas sin penalizar eficiencia energética.

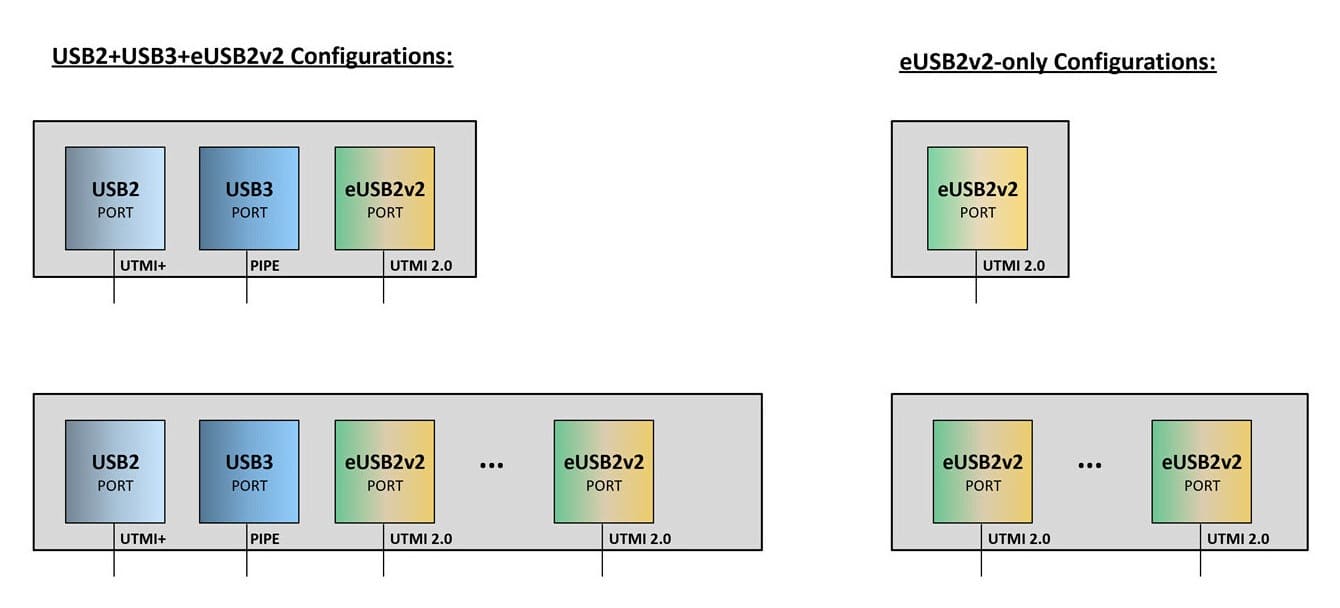

La compañía destaca que su IP eUSB2V2 está pensada para reemplazar USB 2.0 heredado o eUSB2V1, mejorando el equilibrio PPA (rendimiento, potencia y área) y simplificando la integración en diseños complejos. Además, es compatible con UTMI 2.0 y puede convivir con USB 3.2 y USB 2.0, reduciendo riesgos en subsistemas USB completos.

De chip de prueba a solución completa de extremo a extremo

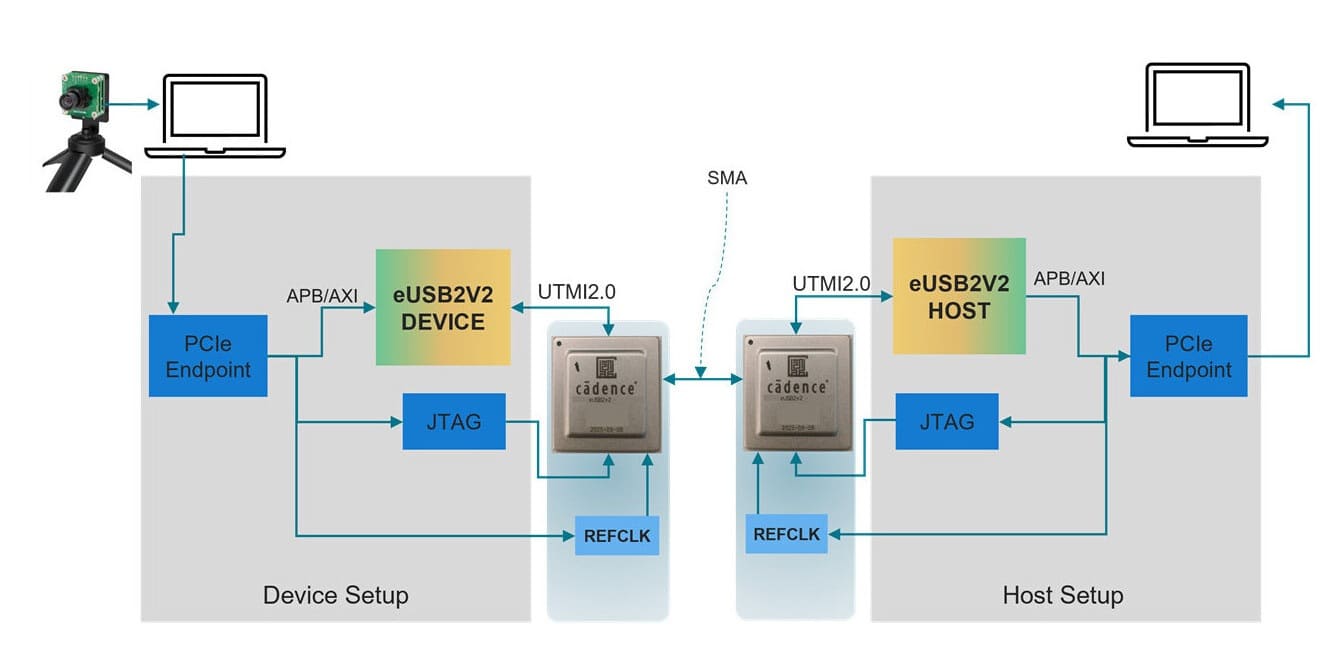

Cadence dio un paso clave a principios de año con el tapeout del primer PHY eUSB2V2 a 3 nm, ya validado y con caracterización de silicio completada. A partir de ahí, la firma ha desarrollado una solución end-to-end que incluye PHYs y controladores tanto de host como de dispositivo.

La compañía adelantó que en CES 2026 mostrará una demo en tiempo real de este sistema completo, integrando PHYs y controladores para evidenciar el rendimiento en escenarios reales. El planteamiento apunta a facilitar la adopción del estándar en PCs con IA y plataformas edge AI sin fricciones de diseño.

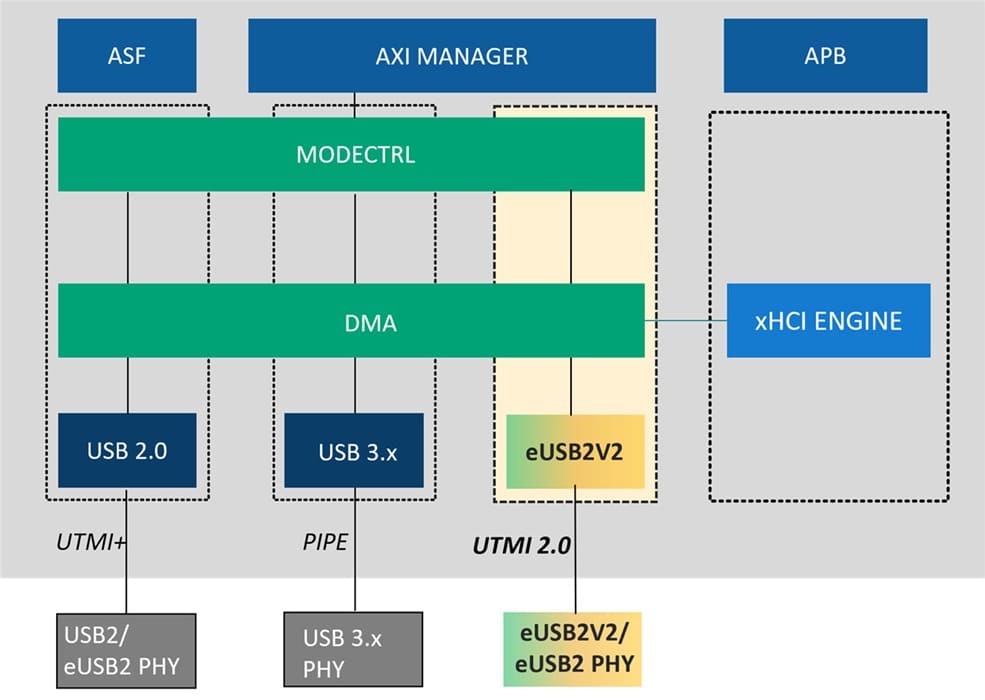

Controladores eUSB2V2: foco en flexibilidad y ancho de banda

Los controladores eUSB2V2 incorporan mejoras específicas para cargas modernas. Entre ellas, el soporte de múltiples transacciones burst para endpoints isócronos dentro de un micro-frame, lo que maximiza el uso del ancho de banda periódico. También se amplía el MaxPacketSize para endpoints bulk hasta 1.024 bytes, clave para transferencias de datos voluminosas como imágenes de alta resolución.

A nivel energético, se integran técnicas avanzadas de clock gating para reducir consumo, manteniendo la interoperabilidad con puertos USB 2.0 y USB 3.x existentes. El número de puertos eUSB2V2 configurables permite adaptar el diseño tanto si se añade conectividad nueva como si se sustituye un puerto heredado.

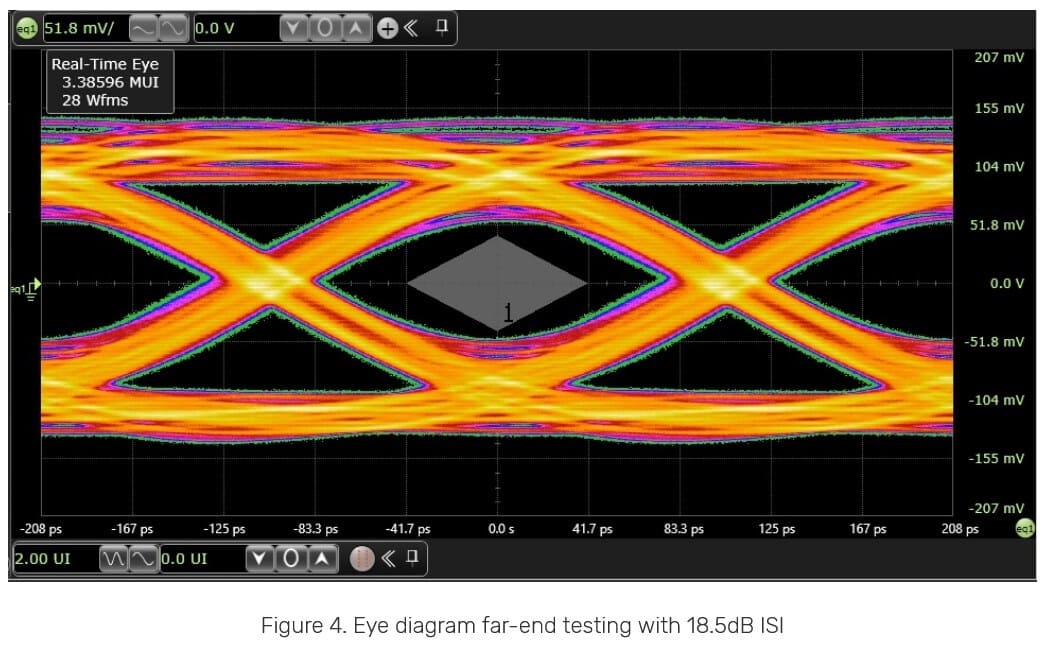

Integridad de señal validada en condiciones exigentes

Para verificar la robustez del enlace, los ingenieros de Cadence realizaron pruebas de eye diagram con 18,5 dB de ISI, obteniendo una señal limpia y estable a 4,8 Gbit/s. Este resultado respalda la fiabilidad del conjunto PHY + controlador en escenarios de alta velocidad, un punto crítico para dispositivos de IA sensibles a errores de transmisión.

En conjunto, la solución eUSB2V2 a 3 nm refuerza el catálogo de IP de interfaces de Cadence junto a USB 3.x, MIPI, DisplayPort, eDP y PCIe. Más allá del avance técnico, el anuncio refleja una tendencia clara: la conectividad de bajo consumo y alta velocidad se convierte en un pilar estratégico para la próxima oleada de PCs con IA y sistemas edge AI.

Vía: TechPowerUp