La compañía Qualitas Semiconductor ha desarrollado una nueva IP PCIe 6.0 PHY, marcando un salto significativo en lo que a tecnología de interconexión de ordenadores se refiere.

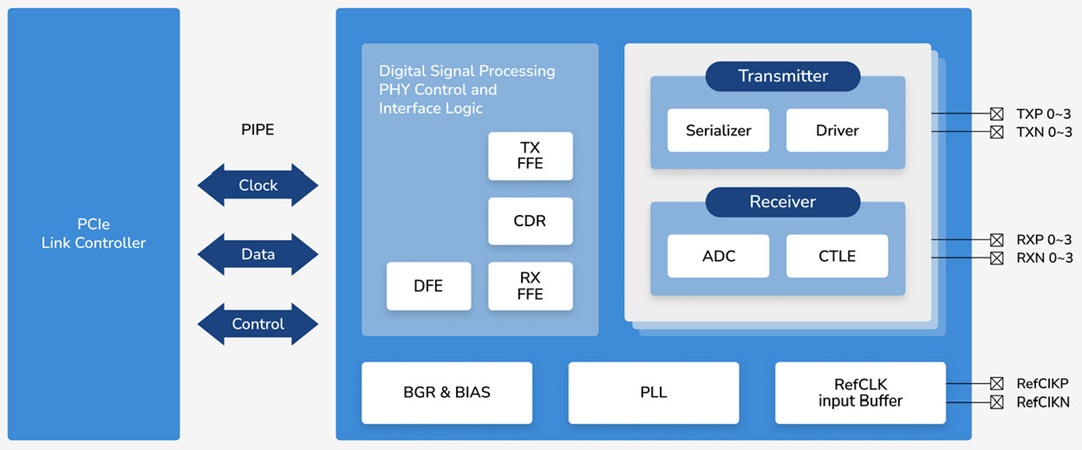

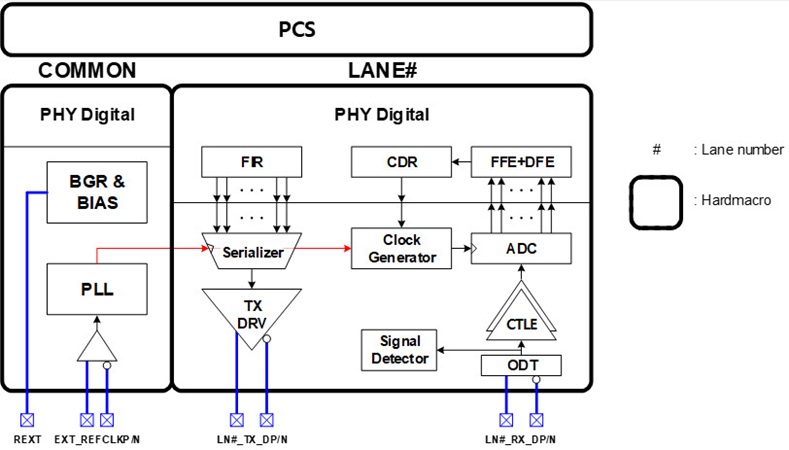

Creado con la avanzada tecnología de proceso de 5 nm, este nuevo producto está diseñado para dar respuesta a las necesidades de transferencia de datos a alta velocidad de la era de la IA. La IP PCIe 6.0 PHY de Qualitas, que se basa en la tecnología CMOS FinFet de 5 nm, consta de un PMA y un PCS hardmacro que cumplen la especificación PCIe Base 6.0.

Esta IP puede alcanzar velocidades de transmisión de hasta 64GT/s por cada línea. Cuando se hace uso de las 16 líneas, puede transferir datos a velocidades de hasta 256 GB/s. Tales velocidades la hacen idónea para centros de datos y tecnologías de conducción autónoma, donde el veloz procesamiento de datos resulta vital.

La empresa ha logrado dicho rendimiento implementando la tecnología de señalización 100G PAM4. El CEO de Qualitas, Dr. Duho Kim, destacó la trascendencia de la nueva IP y señaló la firme voluntad de la firma de seguir superando los límites de la tecnología de semiconductores.

Características más destacadas:

- Tecnología de dispositivos CMOS mejorada de bajo consumo de 5 nm

- 1,8 V ± 5%, 0,85 V ± 5% doble alimentación

- Cumple las especificaciones PCIe Base 6.0 y PIPE 6.1

- Compatible con Gen 1, Gen 2, Gen 3, Gen 4, Gen 5 y Gen 6

- Configuración de canales para vías de datos

- Común (CMN) y 1, 2 ó 4 vías de datos

- Admite los correspondientes niveles de preénfasis del transmisor

- -3,5 / -6 dB para Gen 1 y Gen 2

- Multi-tap FIR con resolución de 1/63 para Gen 3 a Gen 6

- Admite CTLE, FFE multitap basado en DSP y DFE de 1tap para ecualización de canal en receptor

- Admite ecualización adaptativa de canales

- Se requiere una frecuencia de referencia de 100 MHz (soporte de búfer de entrada diferencial)

- Función de autocomprobación integrada capaz de generar y comprobar patrones PRBS

- PCS incluido en PHY hardmacro

Vía: TechPowerUp