El desarrollo de la memoria HBM5 y HBM6 ya está en marcha mientras la industria prepara la transición hacia HBM4 en producción masiva. La firma surcoreana Hanmi Semiconductor ha presentado los primeros Wide TC Bonders, equipos diseñados específicamente para el ensamblado avanzado de estas nuevas generaciones, con mejoras clave en rendimiento de fabricación, eficiencia energética y densidad por apilado.

La evolución llega en paralelo a los futuros aceleradores de NVIDIA, como la arquitectura Feynman, y a las próximas plataformas Instinct MI500 de AMD, que dependerán de memorias de ultra alto ancho de banda para alimentar cargas de IA, entrenamiento de modelos y movimiento de datos a escala de centro de datos.

Wide TC Bonder: alternativa al Hybrid Bonder en la producción de HBM

El nuevo Wide TC Bonder se posiciona como alternativa al tradicional Hybrid Bonder, cuya implementación ha sufrido retrasos técnicos en fases previas. Según los datos adelantados para Semicon Korea 2026, este equipo permitirá mejorar el rendimiento de fabricación en estándares como HBM4, HBM4E, HBM5 y HBM6, reduciendo defectos en el encapsulado y optimizando la precisión del ensamblado.

Uno de los avances más relevantes es la adopción de tecnología de unión sin fundente (fluxless bonding), que elimina la necesidad de materiales auxiliares y reduce la capa de óxido en la superficie del chip. Este enfoque incrementa la resistencia del enlace, mejora la integridad estructural y contribuye a disminuir el grosor total del apilado HBM, algo crítico en configuraciones de alta densidad.

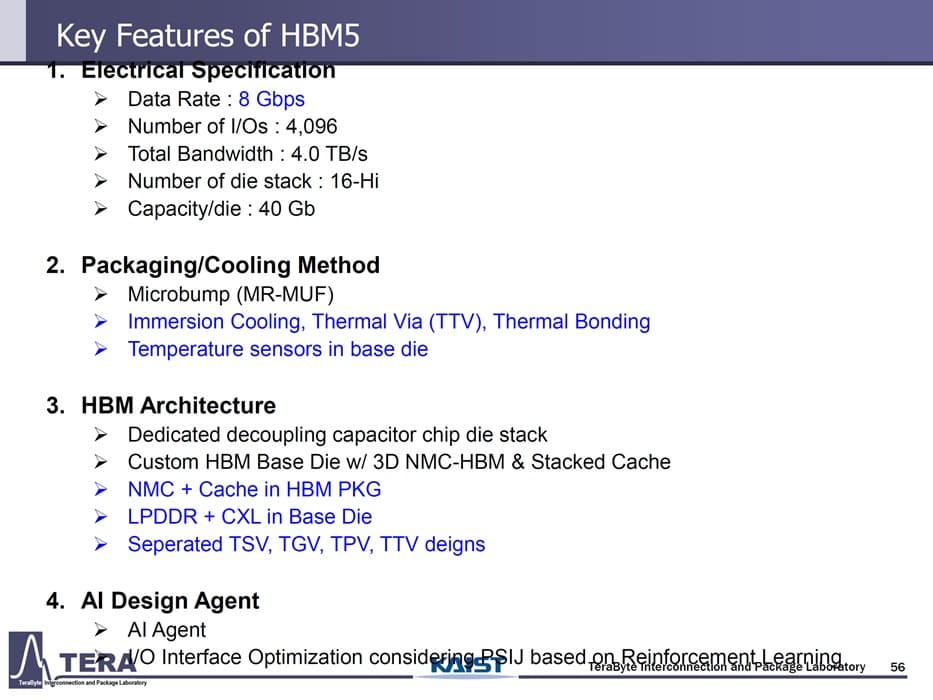

HBM5: 4 TB/s por stack y hasta 80 GB de capacidad

La especificación preliminar de HBM5 mantiene una tasa de transferencia de 8 Gbps, pero amplía el bus a 4.096 bits de I/O, alcanzando un ancho de banda total de 4 TB/s por stack. El diseño base contempla configuraciones de 16-Hi, con chips DRAM de 40 Gb, lo que permite escalar hasta 80 GB por apilado.

En términos energéticos, cada módulo podría situarse en torno a 100W por stack, integrando encapsulado Microbump (MR-MUF) y soluciones de refrigeración por inmersión. Además, se contemplan innovaciones como Base Die personalizado con 3D NMC-HBM, memoria cache apilada, integración de LPDDR + CXL en el Base Die y condensadores dedicados para desacoplo eléctrico.

HBM5 apunta directamente a futuras GPU basadas en NVIDIA Feynman y plataformas Instinct MI500, con un lanzamiento comercial estimado hacia 2029.

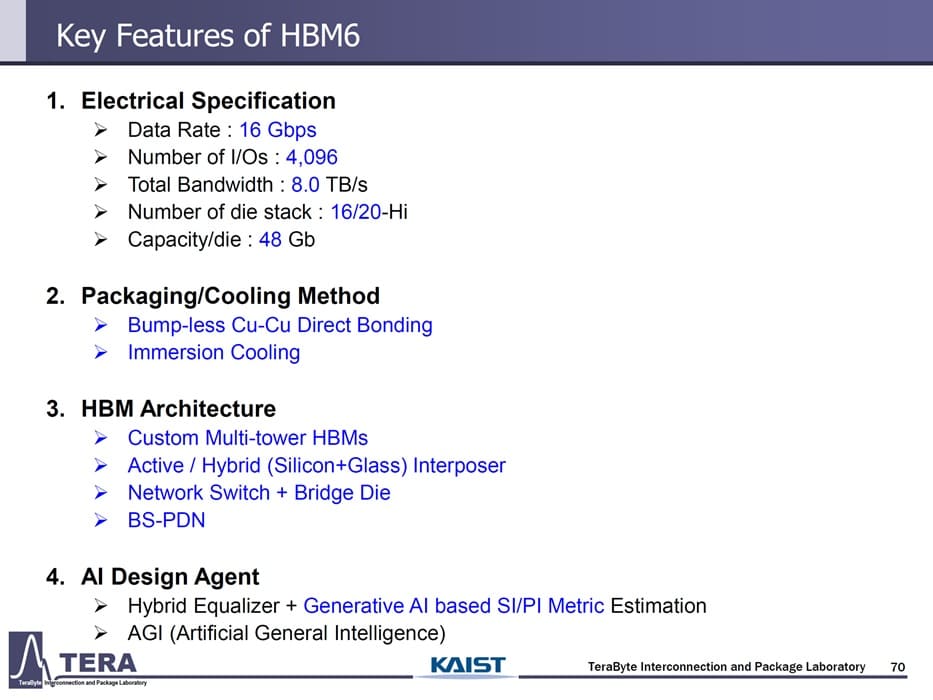

HBM6: 8 TB/s y hasta 120 GB por stack

La siguiente iteración, HBM6, duplicará el ancho de banda hasta 8 TB/s por stack, elevando la velocidad a 16 Gbps y aumentando la capacidad por chip hasta 48 Gb. Se espera que esta generación supere el límite tradicional de 16-Hi, alcanzando configuraciones de 20-Hi.

Esto permitiría escalar la capacidad entre 96 GB y 120 GB por apilado, con un consumo estimado de 120W por stack. En el apartado técnico, se adoptará Bump-less Cu-Cu Direct Bonding, junto a una arquitectura de interposer Active/Hybrid (Silicon + Glass) y configuraciones multi-torre HBM en fase de investigación.

Entre las tecnologías en desarrollo destacan la integración de conmutador de red integrado en encapsulado, Bridge Die dedicado y diseños con TSV asimétricos, pensados para maximizar la eficiencia en entornos de mini centro de datos y aceleradores de próxima generación.

Con HBM4 entrando en producción este mismo año, la hoja de ruta deja claro que la escalada en ancho de banda, capacidad por apilado y potencia energética continuará acelerándose. La memoria de alto ancho de banda sigue siendo un componente crítico dentro del sector de GPU, y HBM5 y HBM6 marcan el siguiente salto evolutivo para el sector de semiconductores.

Vía: Wccftech