Micron ha comenzado el envío de muestras del módulo SOCAMM2 de 256 GB, basado en LPDDR5X monolítica de 32 Gb, una solución orientada a servidores de IA y HPC donde la capacidad por Socket y el consumo energético por nodo se han convertido en limitaciones estructurales. En plataformas con CPU octa-channel, la configuración puede escalar hasta 2 TB de LPDRAM por Socket, una cifra que responde al crecimiento sostenido de modelos y cargas de inferencia.

El movimiento se produce en un contexto en el que la IA generativa, la inferencia en tiempo real y los entornos de computación científica contemporánea están elevando el tamaño de los modelos, ampliando las ventanas de contexto y consolidando el uso de caché KV persistente en memoria. En centros de datos con restricciones de potencia y refrigeración, la memoria deja de ser un componente secundario y pasa a definir la arquitectura del sistema.

LPDDR5X monolítica y salto de densidad por Socket

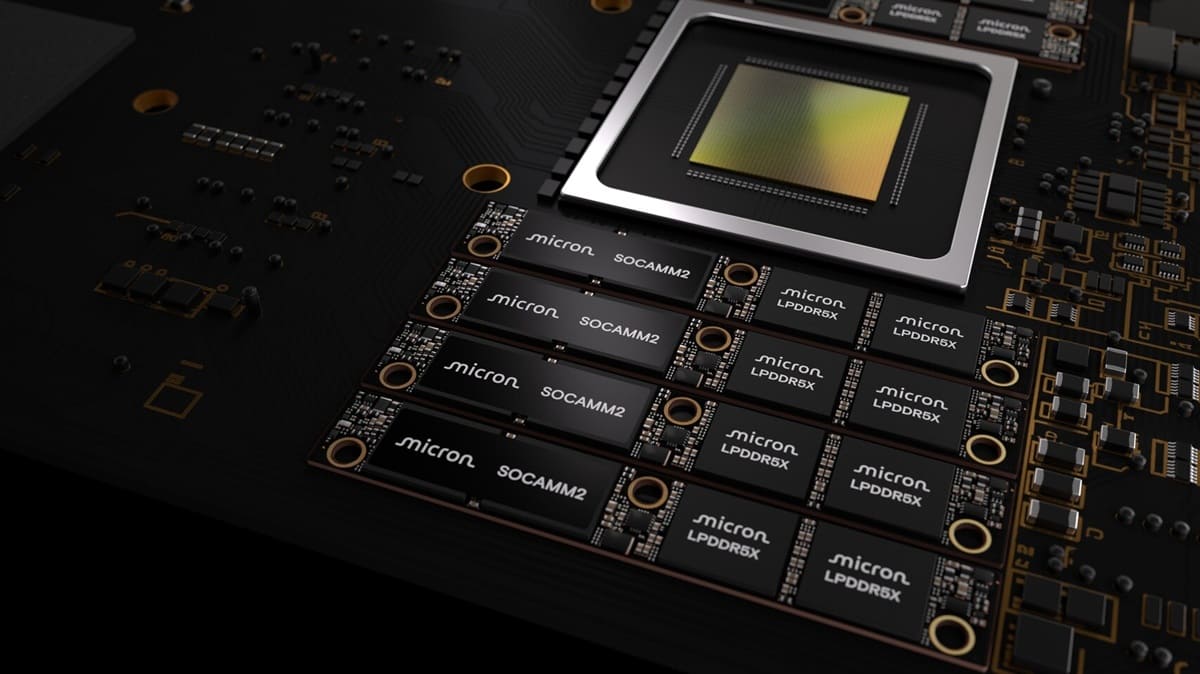

El nuevo SOCAMM2 de 256 GB utiliza un diseño LPDDR5X monolítico de 32 Gb, lo que permite incrementar la densidad por módulo frente a la generación anterior de 192 GB. En configuraciones octa-channel, es posible alcanzar 2 TB de LPDRAM por Socket, reduciendo la necesidad de accesos a almacenamiento externo en cargas de inferencia continua y procesamiento de modelos de gran tamaño.

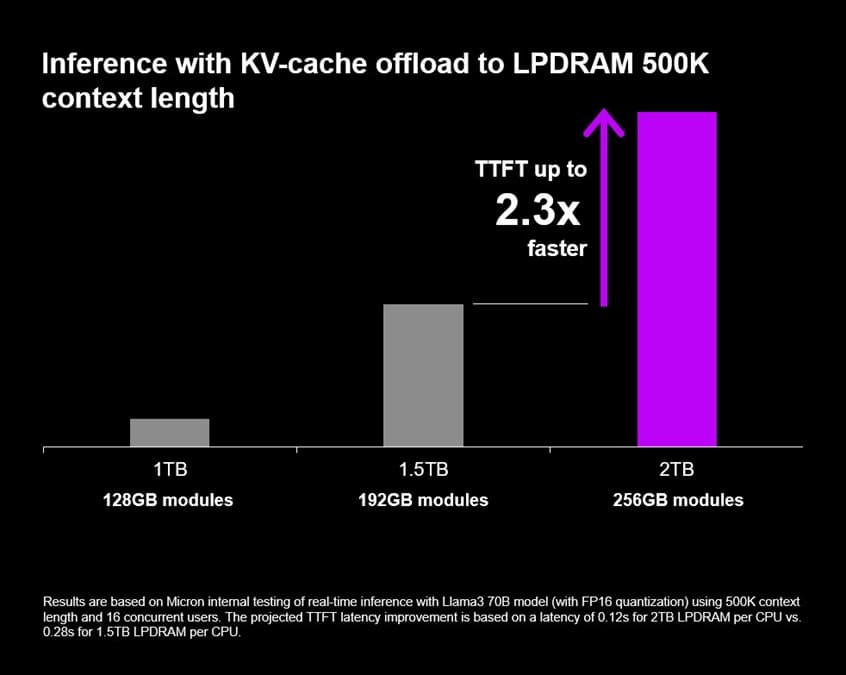

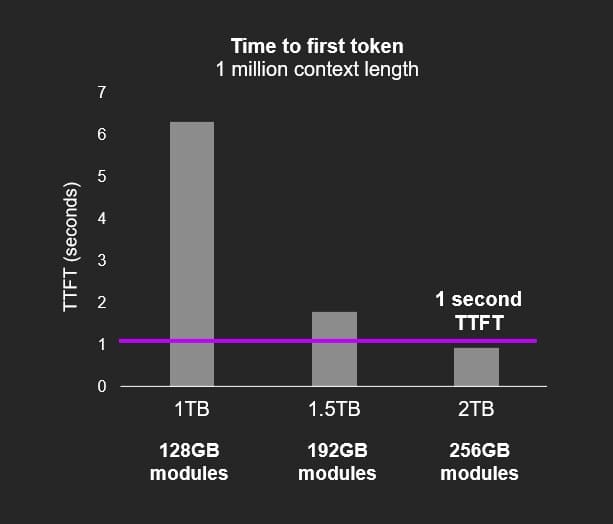

La relevancia no está únicamente en la cifra total. En arquitecturas con memoria unificada, mantener la caché KV cerca del procesador reduce latencia efectiva y mejora el tiempo hasta el primer token en servicios de LLM de contexto largo. Este tipo de optimización impacta directamente en experiencia de usuario y eficiencia de infraestructura en despliegues comerciales.

En el sector de semiconductores, la escalabilidad ya no depende solo del silicio de CPU, sino del equilibrio entre capacidad instalada, ancho de banda efectivo y consumo por vatio dentro del subsistema de memoria.

Consumo energético y densidad por rack

Micron señala que el SOCAMM2 de 256 GB puede operar con aproximadamente un tercio del consumo de módulos RDIMM equivalentes, ocupando además un tercio del espacio físico. En términos prácticos, esto permite aumentar la densidad por rack o reducir el coste energético operativo, dos variables críticas en centros de datos de última generación.

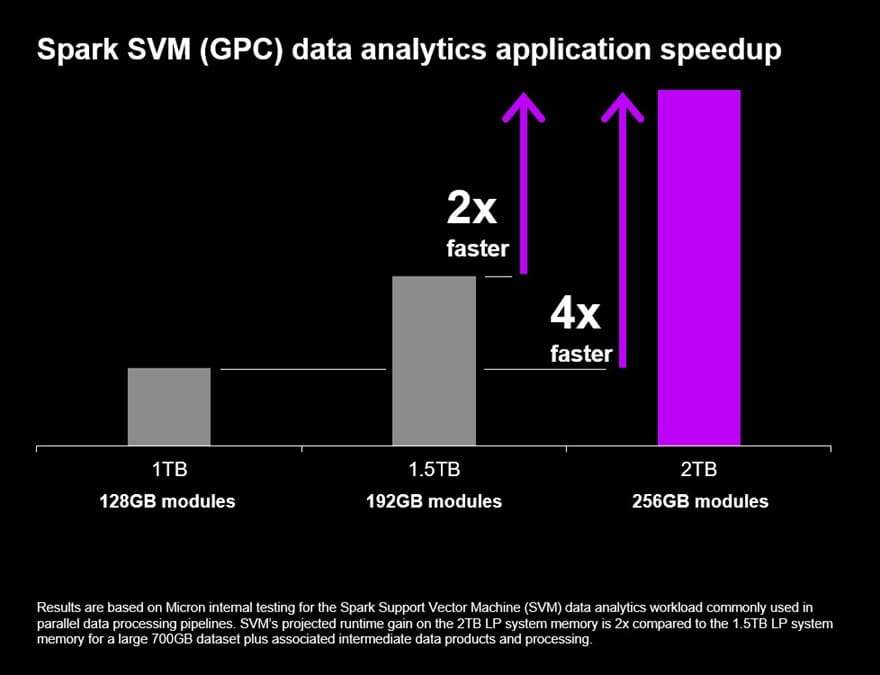

En cargas centradas en CPU, el módulo puede ofrecer hasta 3 veces mejor rendimiento por vatio frente a memoria generalista. En escenarios con LLM de gran contexto, el uso del módulo para descarga de caché KV puede mejorar el rendimiento en más de 2,3 veces respecto a soluciones disponibles. Aunque el resultado final depende de la arquitectura concreta, la combinación de capacidad elevada y bajo consumo es el eje estructural del diseño.

En entornos con refrigeración líquida y límites térmicos estrictos, reducir la potencia del subsistema de memoria libera margen para otras partes críticas del sistema.

Modularidad, estándar JEDEC y posicionamiento en el mercado

El formato SOCAMM2 modular facilita la mantenibilidad, es compatible con arquitecturas refrigeradas por líquido y permite ampliaciones futuras conforme crezcan las necesidades de IA avanzada y HPC. No se trata solo de un módulo de mayor tamaño, sino de una pieza pensada para integrarse en plataformas escalables y de alta densidad.

Micron participa en la definición de la especificación JEDEC SOCAMM2, reforzando su posicionamiento en el segmento de LPDRAM para servidor. Su cartera abarca componentes de 8 GB a 64 GB y módulos SOCAMM2 de 48 GB a 256 GB, cubriendo desde configuraciones generalistas hasta despliegues de alta densidad.

En términos estratégicos, el envío del SOCAMM2 de 256 GB refleja una tendencia clara en el sector de IA: la memoria de ultrabajo consumo pasa a ser un elemento estructural en centros de datos contemporáneos. A medida que el crecimiento de los modelos se traslada a entornos comerciales, la eficiencia del subsistema de memoria será determinante para sostener la escalabilidad sin disparar consumo ni costes operativos.

Vía: TechPowerUp