Samsung ha introducido cambios estructurales en su nueva HBM4E centrados en la red de distribución de energía, un punto crítico en memorias apiladas de próxima generación destinadas a aceleradores de IA. El anuncio se produce apenas semanas después de la comercialización de HBM4, capaz de operar de forma sostenida a 11,7 Gbps con margen hasta 13 Gbps, cifras que elevan la exigencia eléctrica y térmica del encapsulado.

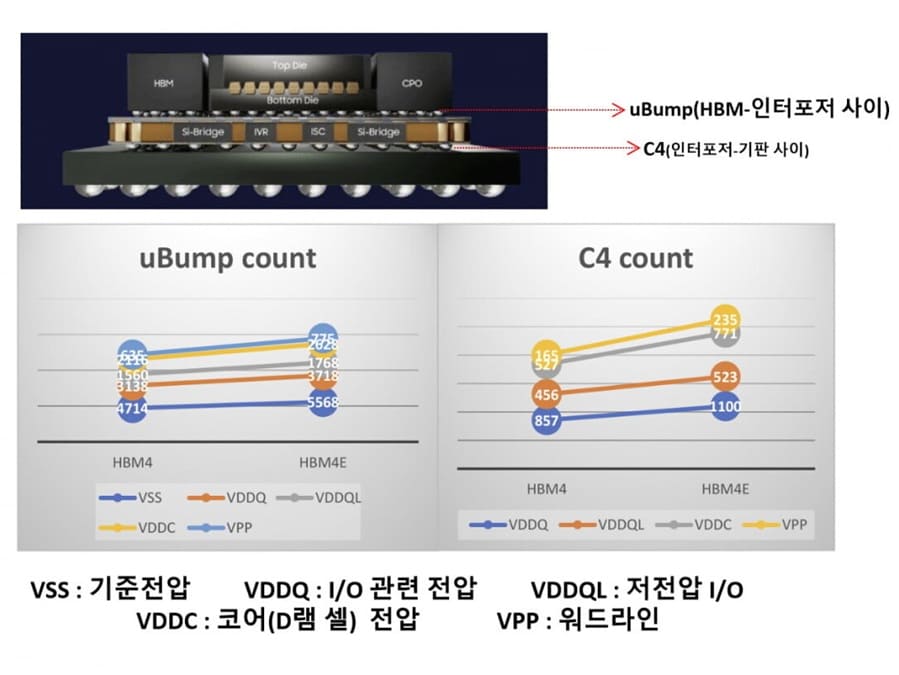

El paso de HBM4 a HBM4E incrementa el número de contactos de alimentación (power bumps) de 13.682 a 14.457, concentrados en el mismo espacio físico y con interconexiones metálicas más finas y densas. Este aumento eleva la densidad de corriente y la resistencia eléctrica interna, intensificando la caída de tensión (IR drop), fenómeno por el cual el voltaje se debilita al atravesar el circuito, especialmente bajo cargas sostenidas de cómputo intensivo.

Más contactos eléctricos y mayor estrés térmico

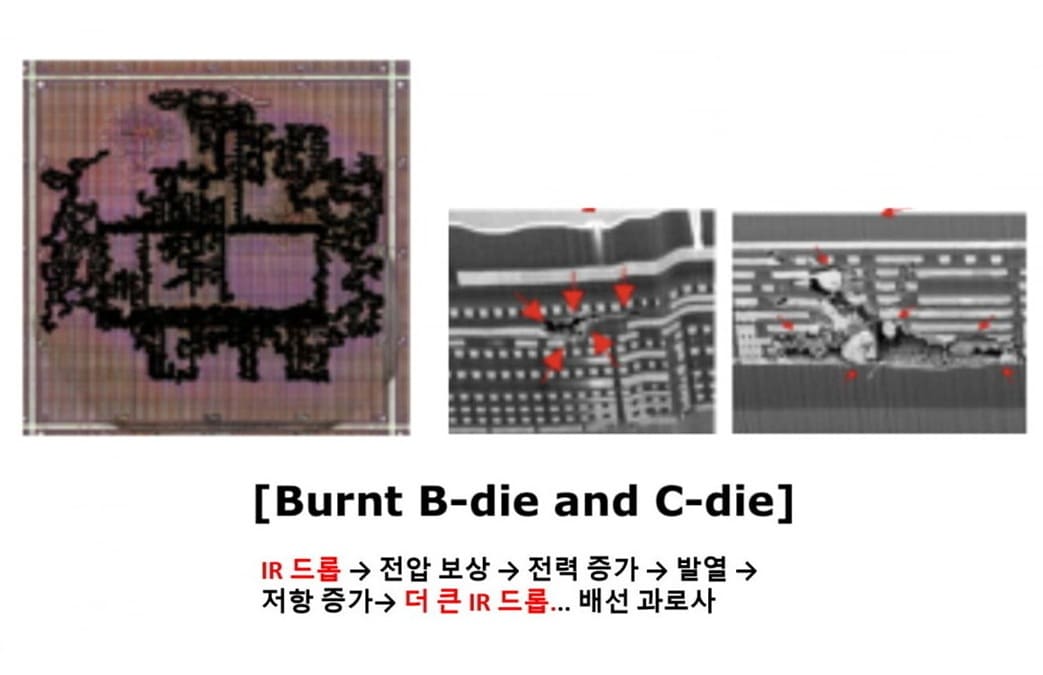

El crecimiento en contactos de alimentación dentro del encapsulado de HBM4E implica una mayor concentración de energía en el mismo volumen. Esta condición incrementa la densidad de corriente, lo que a su vez aumenta la resistencia eléctrica y la generación de calor, creando un efecto acumulativo que puede limitar la estabilidad del sistema.

En configuraciones donde la memoria HBM se sitúa próxima al silicio de GPU, cualquier degradación en la integridad del suministro eléctrico reduce el margen de frecuencia operativa. La combinación de caída de tensión, aumento térmico y carga sostenida en tareas de entrenamiento de modelos multimodales puede afectar tanto al rendimiento como a la fiabilidad a largo plazo.

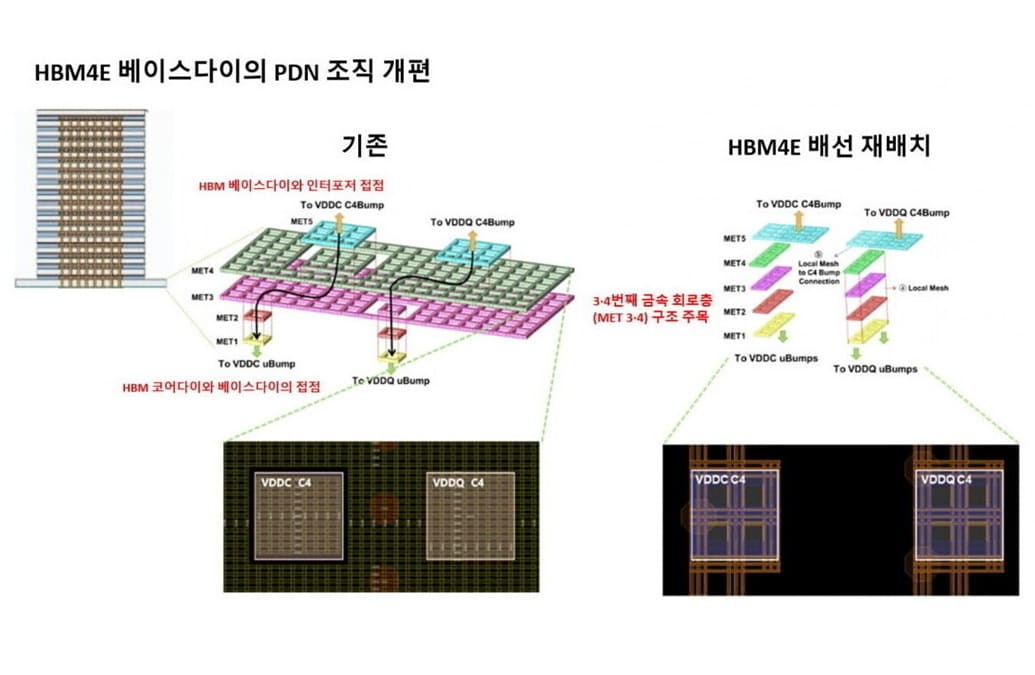

Segmentación de la red de energía en la capa MET4

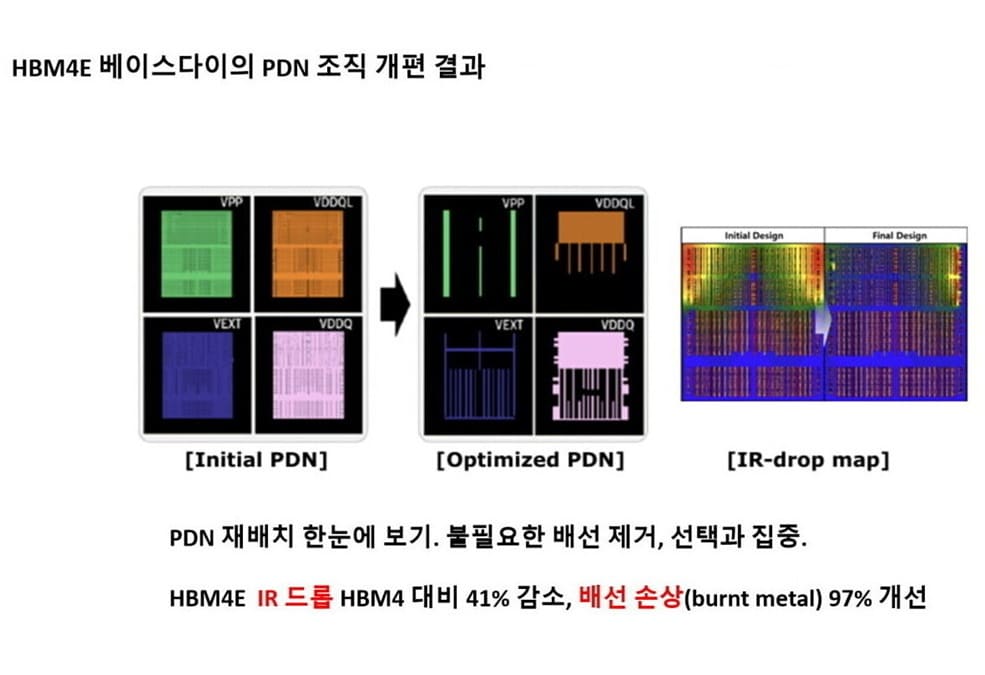

Para mitigar estos efectos, Samsung ha reconfigurado la capa MET4 del dado base, donde se concentra el bloque principal de distribución eléctrica. El anterior diseño centralizado, dispuesto en grandes secciones tipo panal cerca del interposer, ha sido dividido en cuatro bloques independientes, reduciendo congestión y acortando rutas eléctricas.

Además, las capas superiores han sido fragmentadas para optimizar el trazado del cableado metálico y disminuir trayectorias largas que favorecen pérdidas. Según datos de la compañía, esta reorganización ha permitido reducir en 97% los defectos en circuitos metálicos frente a HBM4 y mejorar la caída de tensión (IR drop) en un 41%, ampliando el margen de voltaje disponible para operar a mayores velocidades con mejor estabilidad.

Desde una perspectiva de ingeniería eléctrica, esta mejora no solo aumenta la fiabilidad, sino que libera margen para sostener transferencias cercanas a 13 Gbps sin comprometer la integridad del encapsulado.

Separar físicamente la HBM del silicio de GPU

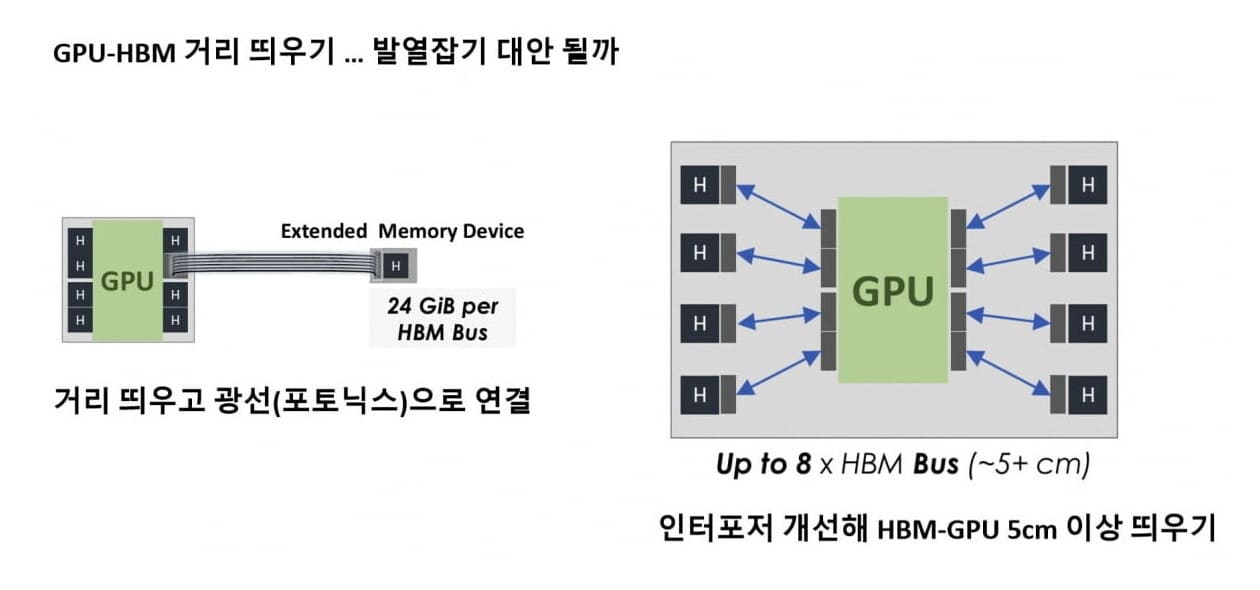

Samsung también estudia una aproximación más radical: separar físicamente la HBM del silicio de GPU para reducir la concentración térmica en el encapsulado avanzado. Tradicionalmente, la memoria de alto ancho de banda se sitúa lo más cerca posible del procesador para minimizar latencia y maximizar transferencia.

Una posible solución pasa por interconexiones fotónicas, capaces de transmitir datos mediante señales ópticas a velocidades de terabits por segundo, compensando la mayor distancia física entre memoria y cómputo. Este enfoque permitiría mantener ancho de banda elevado sin depender exclusivamente de interconexiones de cobre de alta densidad.

La compañía sugiere que avances en el cableado del sustrato podrían permitir ubicar la memoria a más de 5 cm del procesador, reduciendo problemas térmicos asociados a la integración extrema de memoria y lógica en un mismo punto.

Implicaciones en el sector de IA y empaquetado avanzado

El rediseño de HBM4E demuestra que el principal desafío en memorias de próxima generación no es únicamente aumentar los Gbps, sino garantizar estabilidad eléctrica y térmica bajo cargas sostenidas de IA. En el actual sector de IA, donde el entrenamiento masivo exige ancho de banda continuo y estable, la optimización de la red de energía se convierte en un factor diferencial.

Si la segmentación eléctrica y la separación física entre memoria y silicio de GPU se consolidan, el empaquetado avanzado podría evolucionar hacia arquitecturas menos centradas en proximidad extrema y más orientadas a equilibrio térmico y escalabilidad eléctrica. La competencia en HBM de próxima generación se juega tanto en velocidad como en diseño de potencia y fiabilidad a largo plazo.

Vía: TechPowerUp