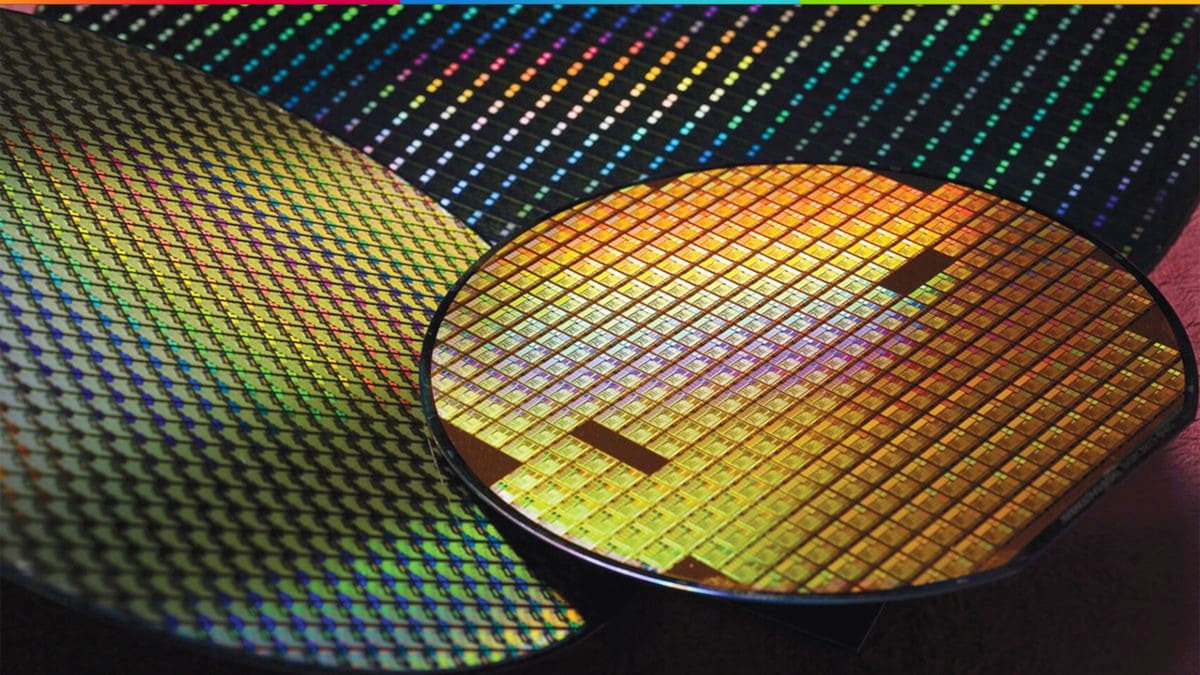

Cadence ha anunciado avances clave en automatización de diseño electrónico (EDA) e intelectual property (IP) gracias a su estrecha colaboración con TSMC. Esta alianza permite a los clientes acelerar el desarrollo de chips para inteligencia artificial (IA) y computación de alto rendimiento (HPC) sobre procesos de última generación como N3, N2 y A16.

Entre las herramientas de Cadence certificadas para estos nodos se encuentran Innovus Implementation System, Quantus Extraction Solution, Tempus Timing Solution, Pegasus Verification System, Liberate Characterization Portfolio, Voltus IC Power Integrity Solution, Genus Synthesis Solution, Virtuoso Studio y Spectre Simulation Platform. Además, ambas compañías trabajan en el desarrollo de flujos de diseño para el proceso A14, cuyo primer PDK llegará a finales de 2025.

Diseño de chips impulsado por IA

Una de las áreas más destacadas es el diseño asistido por IA, que optimiza automáticamente potencia, rendimiento y área (PPA). Con Cadence JedAI Solution, Cerebrus Intelligent Chip Explorer e Innovus+ AI Assistant, los clientes pueden acelerar la creación de chips en TSMC N2, reduciendo tiempos de cierre de diseño mediante funciones como la corrección automática de violaciones DRC.

Esta integración de IA busca no solo mejorar la eficiencia de los equipos de diseño, sino también garantizar que los chips destinados a IA y HPC alcancen el máximo potencial en los procesos más avanzados de TSMC.

Productividad en diseños 3D-IC

Cadence también ha reforzado su soporte para empaquetados avanzados y arquitecturas 3DIC dentro de la plataforma TSMC 3DFabric. Las últimas mejoras incluyen automatización en conexiones bump, implementación física para múltiples chiplets y optimización de alineación mediante IA.

Con herramientas como Clarity 3D Solver y Sigrity X Platform, junto con el Celsius Thermal Solver, los ingenieros pueden realizar análisis SI/PI a nivel de sistema con flujos 3Dblox, reduciendo riesgos térmicos y eléctricos en diseños complejos.

Nuevos IP en TSMC N3P

En el terreno de los IP certificados en N3P, Cadence ha presentado soluciones clave para superar el “muro de memoria” en cargas de trabajo de IA y modelos de lenguaje a gran escala. Entre ellas destacan:

- Primer IP HBM4 en N3P.

- Interfaces LPDDR6/5X a 14.4 Gbps y DDR5 12.8G MRDIMM Gen 2.

- PCIe 7.0 IP a 128 GT/s y SerDes 224G para infraestructura de IA.

- eUSB2V2 y UCIe 32G IP, fundamentales para ecosistemas de chiplets y AI PC.

Estas innovaciones aseguran mayor ancho de banda, escalabilidad y eficiencia energética en sistemas destinados a IA y centros de datos.

Conclusión

La colaboración entre Cadence, TSMC y el ecosistema OIP representa un paso decisivo para acelerar la superciclo de la IA, ofreciendo a los clientes herramientas y soluciones que integran IA, 3D-IC y IP de última generación, reduciendo la complejidad del diseño y mejorando el rendimiento energético de los chips del futuro.

Vía: TechPowerUp