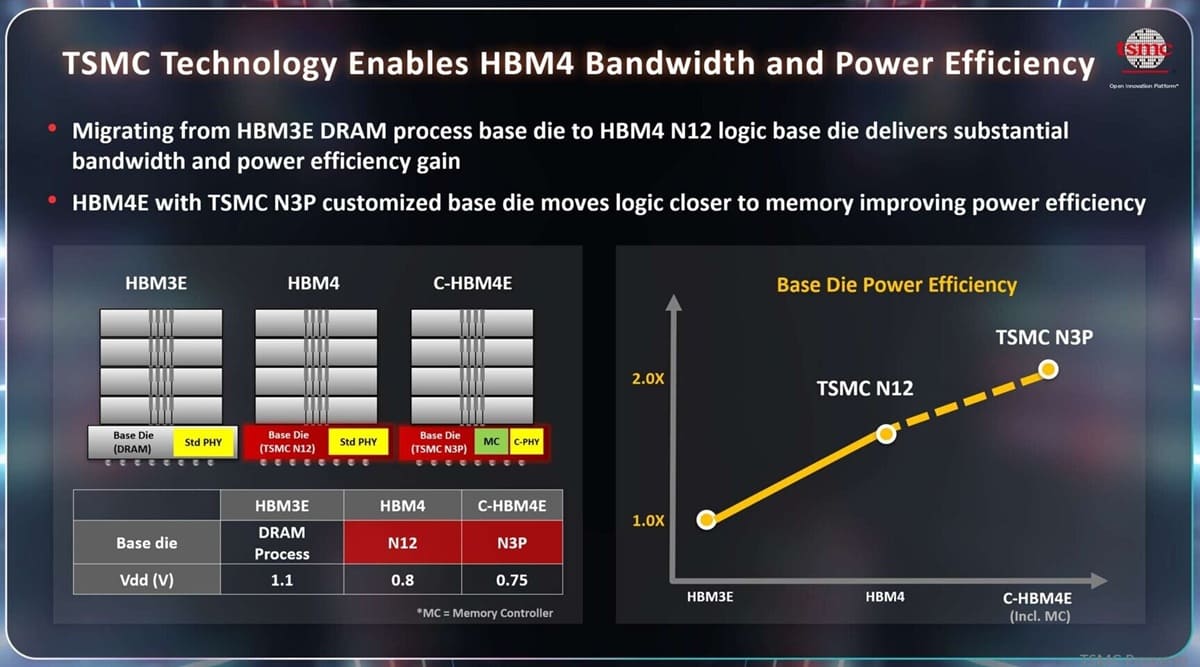

Durante el Open Innovation Platform Ecosystem Forum celebrado en Ámsterdam, TSMC ofreció nuevos detalles sobre su próxima generación de memoria HBM4 personalizada, según ha informado HardwareLUXX. La compañía está desarrollando un C-HBM4E con die lógico N3P y una reducción de voltaje de 0,8 V a 0,75 V, lo que permitirá duplicar la eficiencia energética frente a los procesos actuales de DRAM. Además, incluso las bases estándar de HBM4 verán mejoras notables: en lugar de emplear un proceso DRAM convencional como en HBM3E, se fabricarán en el nodo lógico N12, reduciendo la tensión operativa de 1,1 V a 0,8 V y aumentando la eficiencia en 1,5×.

El diseño C-HBM4E de TSMC integrará directamente los controladores de memoria dentro del propio stack, una innovación que traslada parte de la lógica antes situada en el SoC principal. Este cambio convierte el PHY en una arquitectura totalmente personalizada, mejorando la gestión de energía y la comunicación entre capas de memoria apilada para futuras GPU y aceleradores de IA.

Evolución de CoWoS y empaquetado avanzado

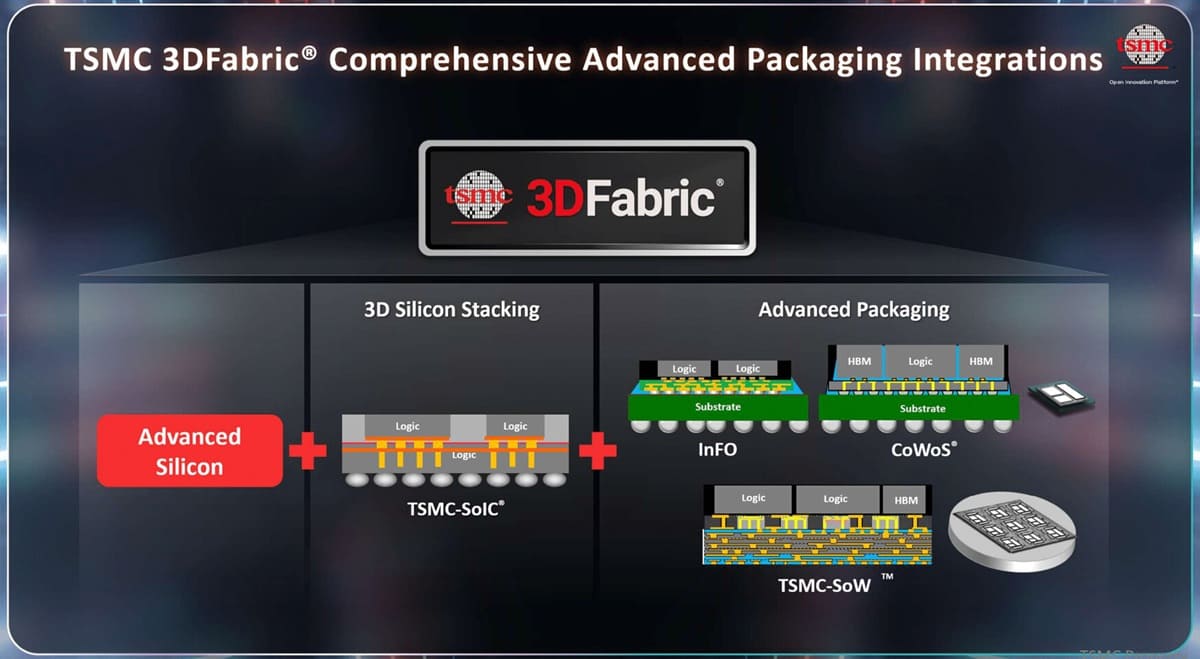

Paralelamente, TSMC amplía su catálogo de encapsulado avanzado con versiones mejoradas de InFO y SoW, aunque CoWoS sigue siendo su principal motor de crecimiento. Tras escalar de 1,5× a 3,3× en tamaño de retícula y soportar hasta ocho chips HBM, la compañía avanza hacia CoWoS-L, una nueva variante que permitirá integrar hasta 12 pilas HBM3E o HBM4 en soluciones de IA previstas para 2026.

Además, TSMC ya trabaja en la siguiente evolución CoWoS-A16, programada para 2027, con un formato aún mayor destinado a plataformas de GPU y TPU de próxima generación. Este enfoque refuerza el liderazgo de la fundición en interconexión 2.5D y 3D, un área clave para satisfacer la demanda de chips heterogéneos de gran tamaño.

Alianzas estratégicas con Micron y SK hynix

La compañía también ha asegurado acuerdos con los principales fabricantes de memoria HBM. Micron ha seleccionado a TSMC para producir los dados lógicos base de sus módulos HBM4E, con inicio de producción en volumen previsto para 2027. Por su parte, SK hynix se prepara para lanzar sus primeros productos HBM4E personalizados en la segunda mitad de 2026, utilizando el proceso de 12 nm de TSMC para versiones de servidor y un nodo de 3 nm en configuraciones destinadas a GPU de NVIDIA y TPU de Google.

Estos acuerdos consolidan a TSMC como pieza central en el ecosistema HBM4, combinando su experiencia en silicio lógico avanzado con capacidades de encapsulado CoWoS-L, justo cuando el sector de IA exige mayor rendimiento y eficiencia energética para los aceleradores de próxima generación.

Vía: TechPowerUp