NVIDIA estaría explorando nuevas vías para reforzar su posición en el segmento de inferencia de IA, y una de las más relevantes pasa por la posible integración de unidades LPU directamente dentro de la arquitectura Feynman, prevista para la segunda mitad de la década. Aunque no existe confirmación oficial, varios análisis técnicos apuntan a que la compañía quiere ir más allá del enfoque clásico basado únicamente en GPU.

El movimiento se enmarca en el acuerdo de licencia de propiedad intelectual con Groq, centrado en tecnologías de Language Processing Units, una señal clara de que NVIDIA busca controlar todo el stack de inferencia, desde el silicio hasta el software, en un mercado cada vez más competitivo.

Hybrid bonding como vía de integración

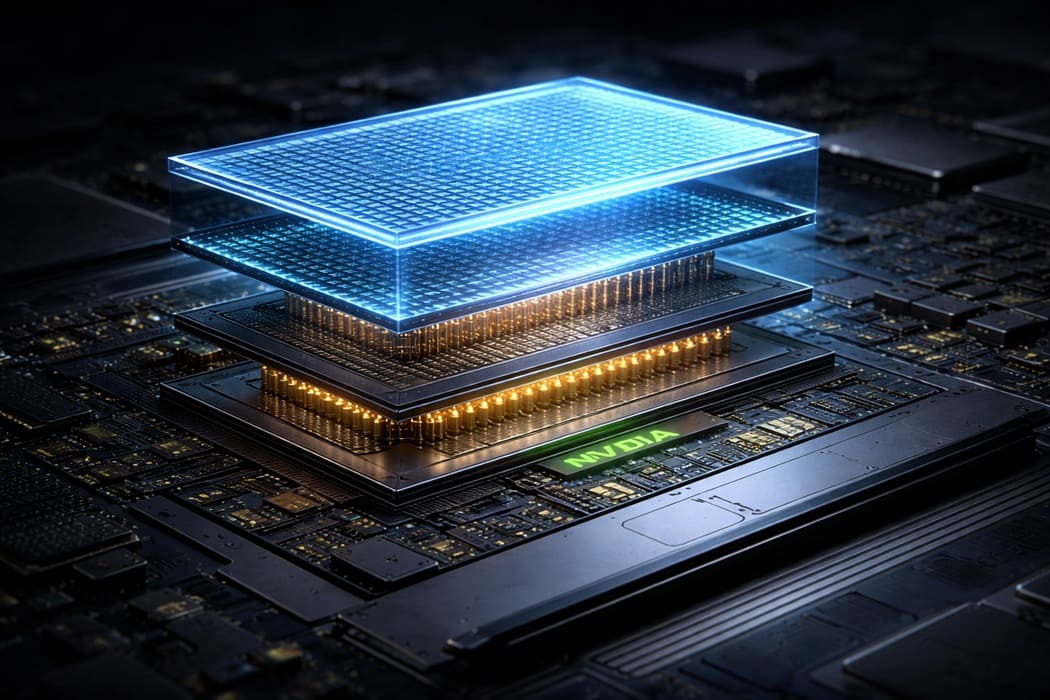

Según el analista técnico AGF, una de las opciones más plausibles para NVIDIA sería apilar dies LPU sobre el die principal de Feynman utilizando la tecnología de hybrid bonding de TSMC. Este enfoque permitiría conectar grandes bancos de SRAM con una interfaz mucho más amplia y eficiente que la memoria externa convencional.

El planteamiento recuerda a la estrategia empleada por AMD con sus CPU X3D, donde el uso de SoIC (System on Integrated Chips) permite apilar memoria directamente sobre el chip de cómputo. En el caso de NVIDIA, el objetivo no sería añadir caché genérica, sino unidades LPU especializadas para acelerar tareas de inferencia con baja latencia y alto rendimiento sostenido.

Separar cómputo y SRAM para optimizar costes

Uno de los puntos clave del análisis es evitar integrar SRAM monolítica en nodos avanzados. La escalabilidad limitada de la SRAM hace que fabricarla en procesos punteros resulte ineficiente y costoso, desperdiciando área de silicio de alto valor. Por ello, la propuesta pasa por usar nodos avanzados como A16 (1,6 nm) únicamente para el die de cómputo, que albergaría Tensor Cores, lógica de control y bloques críticos.

Las LPUs apiladas se encargarían de los grandes bancos de SRAM, conectadas mediante hybrid bonding. Además, el uso de backside power delivery en A16 liberaría espacio en la cara frontal del chip, facilitando interconexiones verticales de memoria con menor latencia y menor consumo energético por bit transferido.

Retos térmicos y de ejecución

Este enfoque, sin embargo, no está exento de riesgos. El apilado de dies sobre chips con alta densidad de cómputo plantea serios desafíos térmicos, especialmente cuando las LPUs están diseñadas para mantener throughput sostenido durante largos periodos. La disipación de calor podría convertirse en un cuello de botella crítico.

A nivel de ejecución, también surgen tensiones importantes. Las LPUs priorizan flujos deterministas, mientras que el ecosistema CUDA se basa en un modelo más flexible y abstracto, donde la colocación explícita de memoria no es habitual. Integrar SRAM gestionada de forma explícita dentro de arquitecturas GPU requeriría cambios profundos en el modelo de programación y una optimización extrema del entorno GPU-LPU.

En este contexto, la posible integración de LPUs en Feynman debe interpretarse como una apuesta estratégica a largo plazo. Si NVIDIA logra resolver los retos térmicos y de software, podría consolidar una ventaja decisiva en inferencia, incluso a costa de asumir una complejidad de ingeniería sin precedentes.

Vía: Wccftech