Un equipo de investigadores en Francia ha presentado la primera memoria híbrida capaz de realizar tanto entrenamiento como inferencia en sistemas de IA de borde, combinando capacitores ferroeléctricos (FeCAPs) y memristores en un mismo diseño.

Con esta arquitectura híbrida, publicada en Nature Electronics bajo el título “A Ferroelectric-Memristor Memory for Both Training and Inference”, se rompe una limitación histórica en el desarrollo de hardware de IA: la imposibilidad de entrenar modelos localmente en dispositivos de bajo consumo sin depender de sistemas externos o de la nube.

El reto de la IA en el borde

La IA en el edge requiere tanto inferencia (lectura de datos y toma de decisiones) como aprendizaje (actualización de modelos). Hasta ahora, cada tecnología de memoria ofrecía solo una de estas ventajas:

- Memristores: eficientes en inferencia, capaces de almacenar pesos en forma analógica y operar con bajo consumo, pero poco precisos para actualizaciones progresivas.

- FeCAPs: permiten actualizaciones rápidas y de bajo consumo, pero sus lecturas son destructivas, lo que las hacía inadecuadas para inferencia.

Esto obligaba a los diseñadores a elegir entre dispositivos con buena inferencia y entrenamiento en la nube, o entrenamientos locales poco prácticos y de corta vida útil.

La solución híbrida

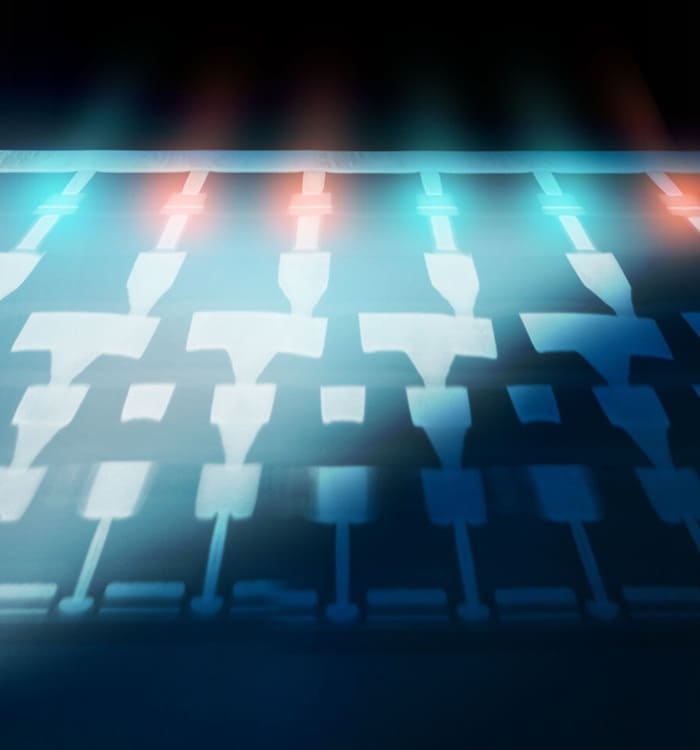

El nuevo enfoque combina ambos elementos en un único stack de memoria CMOS:

- Los memristores almacenan pesos analógicos para la inferencia.

- Los FeCAPs gestionan las actualizaciones con mayor precisión digital.

- De forma periódica, los memristores se reprograman en función de los bits más significativos guardados en los FeCAPs, manteniendo eficiencia y exactitud.

Este sistema se fabricó en un array de 18.432 dispositivos bajo tecnología CMOS de 130 nm, demostrando viabilidad práctica y compatibilidad industrial.

Implicaciones para la industria

La memoria híbrida permite que dispositivos de borde, como vehículos autónomos, sensores médicos o sistemas industriales, realicen aprendizaje en tiempo real con bajo consumo y sin desgaste acelerado del hardware. De este modo, los modelos pueden adaptarse sobre la marcha a nuevos datos, sin necesidad de recurrir constantemente a la nube.

El proyecto estuvo liderado por CEA-Leti, con participación de instituciones como la Université Grenoble Alpes, CEA-List, CNRS, Universidad de Burdeos, IMS France, Université Paris-Saclay y el C2N.

Una vía hacia chips más autónomos

Este avance abre la puerta a memorias multifuncionales capaces de equilibrar entrenamiento e inferencia en el mismo chip, algo que hasta ahora se consideraba inviable en dispositivos de bajo consumo. El desarrollo podría acelerar la llegada de sistemas de IA más autónomos y eficientes en sectores críticos donde la conectividad con la nube no siempre es posible o práctica.

Vía: TechPowerUp