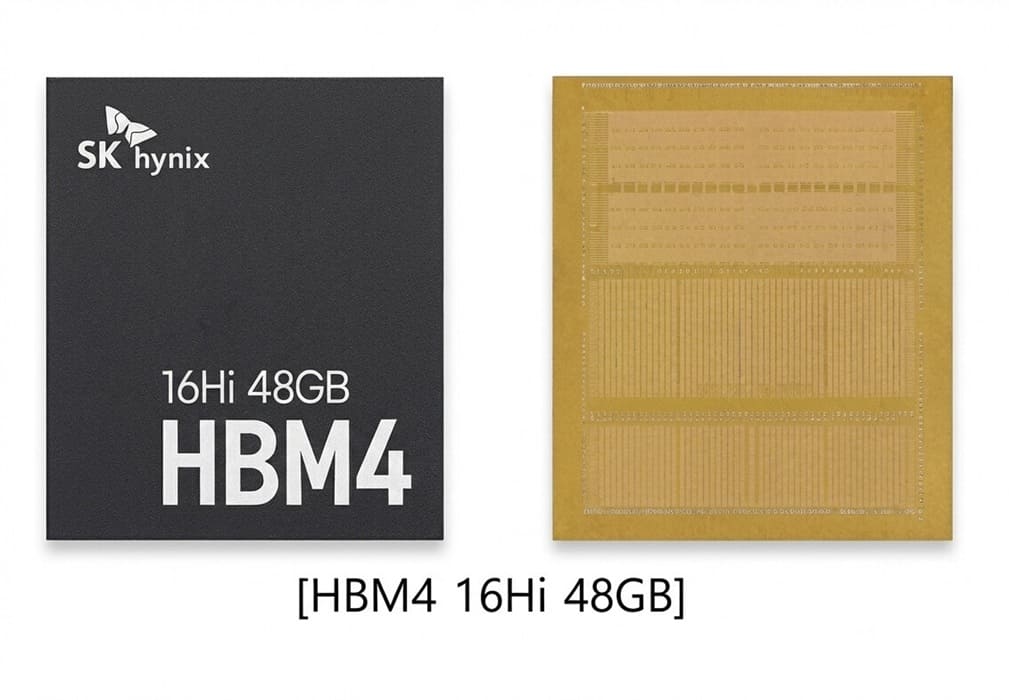

SK hynix ha mostrado un nuevo módulo HBM4 de 16 capas y 48 GB, una capacidad que va un paso más allá de las configuraciones de 12 capas y 36 GB vistas hasta ahora. El movimiento apunta claramente a aceleradores de IA y HPC con una demanda creciente de capacidad de memoria por paquete, incluso antes de que el estándar HBM4 llegue de forma generalizada al mercado.

A diferencia de demostraciones previas, la compañía no ha facilitado frecuencias ni ancho de banda oficiales para esta variante de 16 capas. En generaciones anteriores, la referencia era un HBM4 de 12 capas funcionando a 11,7 Gbps, por lo que es razonable esperar alguna ganancia adicional al añadir cuatro capas DRAM más, aunque SK hynix evita concretar cifras por ahora.

Más capas, más capacidad, y prudencia en las cifras

La falta de datos públicos sugiere un contexto competitivo en plena evolución. Fabricantes rivales también están afinando sus HBM4 antes de los despliegues comerciales en plataformas de AMD y NVIDIA, lo que deja margen para ajustes de velocidad en función de las necesidades de cada cliente. En ese escenario, priorizar capacidad y flexibilidad puede ser más relevante que cerrar números definitivos demasiado pronto.

En la práctica, un HBM4 de 48 GB por pila permite reducir el número total de stacks necesarios en un acelerador, simplificando el diseño del paquete y mejorando la densidad sin sacrificar ancho de banda agregado.

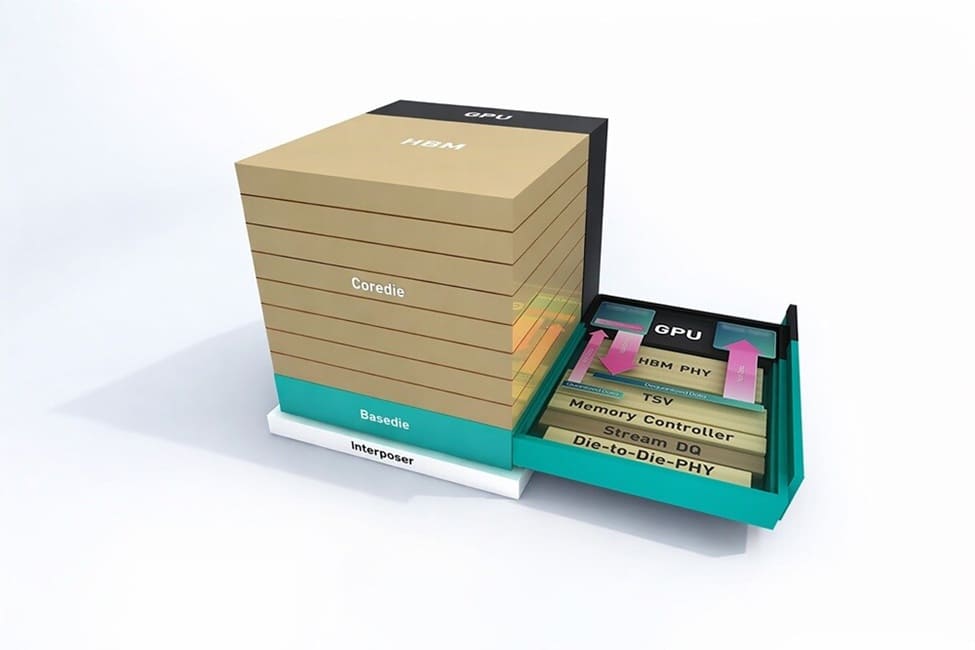

cHBM: mover lógica al “base die” de la memoria

Junto al nuevo stack HBM4, SK hynix también ha mostrado cHBM, un enfoque que introduce un base die personalizado en la parte inferior de la pila de memoria. La idea es trasladar a ese die funciones que normalmente residen en el chip lógico del acelerador, como controladores de memoria, HBM PHY o interfaces die-to-die.

Este cambio tiene dos implicaciones claras. Por un lado, libera área en el silicio principal para más lógica de cómputo. Por otro, abre la puerta a configuraciones a medida, donde el cliente decide qué bloques integrar en la base de la memoria, e incluso insertar lógica de procesamiento dentro del propio stack.

Un diseño más modular para IA y HPC

El planteamiento de cHBM encaja con una tendencia más amplia en el sector: desacoplar funciones y distribuirlas de forma más eficiente entre chiplets y stacks de memoria. En aceleradores de gran tamaño, cada milímetro cuadrado cuenta, y mover bloques “periféricos” al subsistema de memoria puede traducirse en mejor rendimiento por vatio y mayor escalabilidad.

SK hynix no ha anunciado productos comerciales basados en cHBM, pero la demostración deja claro que la compañía está explorando arquitecturas de memoria más activas, pensadas para acompañar la próxima generación de aceleradores de IA y HPC.

Un adelanto de lo que vendrá con HBM4

En conjunto, el HBM4 de 16 capas y 48 GB y el concepto cHBM muestran una hoja de ruta centrada menos en cifras aisladas y más en capacidad, integración y personalización. A medida que los aceleradores sigan creciendo en tamaño y complejidad, estas decisiones de empaquetado y reparto de funciones pueden resultar tan determinantes como el propio ancho de banda.

Vía: TechPowerUp