Samsung y SK hynix estarían siguiendo estrategias diferentes para fabricar la próxima generación de chips DRAM, en un momento marcado por la presión de la IA, los centros de datos y la demanda de memoria HBM. El objetivo común resulta claro: aumentar densidad, mejorar eficiencia y preparar arquitecturas de memoria más complejas para los próximos años.

El contexto resulta especialmente importante. La expansión de servidores para entrenamiento de IA, inferencia avanzada y aceleradores de alto rendimiento está tensionando el suministro de HBM, DRAM y otros componentes que comparten materiales, capacidad fabril y procesos críticos. En ese escenario, dominar el siguiente salto técnico puede convertirse en una ventaja estratégica enorme dentro del sector de semiconductores.

Samsung exploraría una DRAM con enfoque GAAFET

La vía de Samsung pasaría por aplicar conceptos asociados a GAAFET dentro de futuros chips DRAM. En procesadores, esta tecnología envuelve el canal del transistor con la puerta, permitiendo mejor control eléctrico, menores fugas de corriente y más eficiencia frente a diseños tradicionales. Trasladar esa idea a memoria, sin embargo, resulta bastante más complejo.

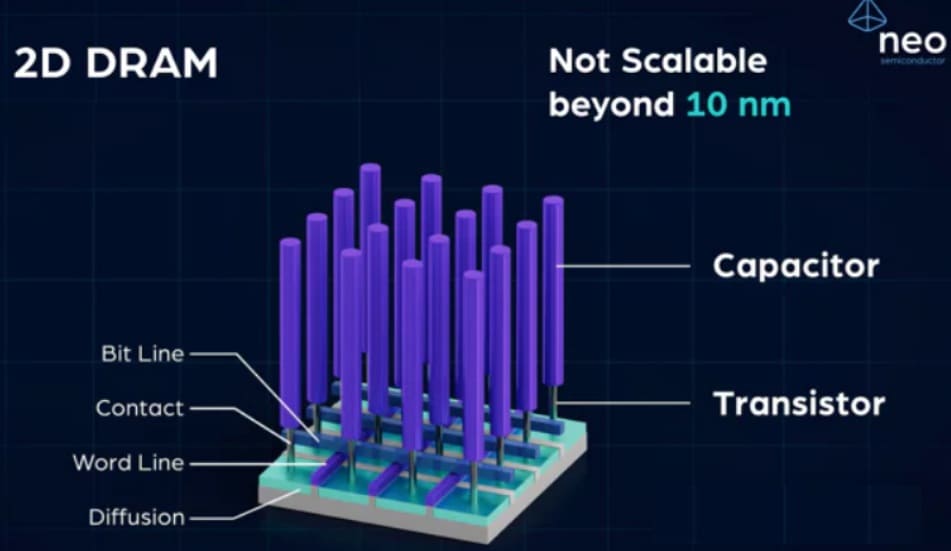

La dificultad viene de la propia naturaleza de la DRAM. A diferencia de un procesador lógico, una celda DRAM combina transistor y condensador, ya que necesita almacenar carga eléctrica para representar datos. A medida que los nodos se reducen, mantener un condensador funcional dentro de una celda cada vez más pequeña se vuelve uno de los grandes cuellos de botella técnicos.

Por eso, Samsung estaría estudiando cómo integrar un transistor GAAFET y un condensador dentro de una misma celda DRAM sin comprometer densidad ni fiabilidad. La idea no consiste solo en reducir tamaño, sino en evitar que la celda pierda capacidad de retención, aumente fugas eléctricas o se vuelva demasiado compleja de fabricar a gran escala.

La influencia de NAND aparece en el diseño de Samsung

Uno de los puntos más llamativos del enfoque de Samsung sería tomar ideas del mundo NAND. La compañía estaría valorando colocar la circuitería encargada de operaciones como lectura y escritura debajo de la matriz de memoria, una técnica similar a la usada en diseños NAND modernos para aprovechar mejor el área del chip.

Ese movimiento tendría sentido si el objetivo pasa por liberar espacio en la parte superior de la estructura. Al desplazar circuitos periféricos bajo la matriz, Samsung podría ganar margen para una celda más compacta, manteniendo elementos clave como el condensador DRAM, el transistor de acceso y las rutas eléctricas necesarias para operar la memoria.

La lectura técnica resulta interesante porque refleja un cruce de tecnologías. Samsung no estaría copiando NAND sin más, sino adaptando una lógica de organización espacial a un tipo de memoria mucho más exigente en retención de carga. La DRAM necesita rapidez, refresco constante y estabilidad eléctrica, por lo que el margen de error resulta mucho menor.

SK hynix apostaría por una estructura 4F² vertical

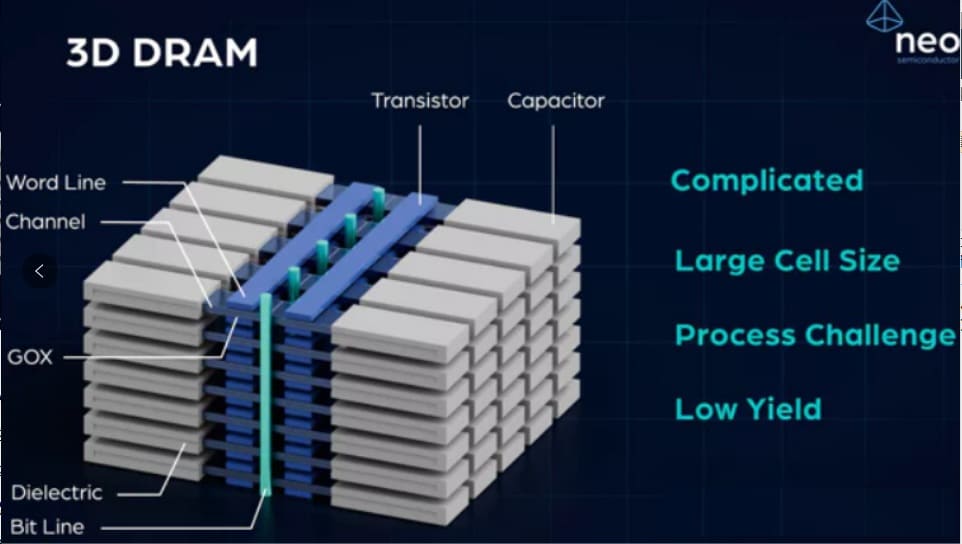

El camino de SK hynix iría en otra dirección, con una aproximación basada en 4F² y transistores apilados verticalmente. En este diseño, el material de puerta envolvería estructuras verticales, buscando una reducción significativa del área ocupada por cada celda y una mayor eficiencia en el escalado de futuras generaciones DRAM.

La ventaja potencial del enfoque 4F² está en la densidad. Si la industria logra reducir el área efectiva de cada celda sin disparar costes, fugas o complejidad, la memoria podría avanzar hacia chips con más capacidad por oblea. Esto resulta especialmente importante en una etapa donde la IA demanda módulos de mayor ancho de banda, más capacidad y mejor eficiencia energética.

El reto, como siempre en memoria, está en llevar el diseño del laboratorio a producción masiva. Apilar transistores, envolverlos con material de puerta y colocar los componentes de lectura bajo el pilar implica desafíos de alineación, uniformidad, rendimiento por oblea y coste industrial. En DRAM, una arquitectura prometedora no basta si no puede fabricarse con tasas de rendimiento competitivas.

La carrera por definir el estándar de la DRAM futura

La competición entre Samsung y SK hynix no se limita a demostrar una tecnología funcional. Ambas compañías buscarían que su enfoque sea reconocido antes como modelo viable para la próxima etapa de DRAM avanzada, algo que puede influir en estándares internos, herramientas de fabricación, inversión fabril y acuerdos con grandes clientes.

Si Samsung logra validar una DRAM basada en ideas GAAFET con organización inspirada en NAND, podría aprovechar parte de su experiencia en nodos avanzados y estructuras de memoria vertical. Si SK hynix impone una vía 4F² más eficiente, reforzaría su posición en un mercado donde ya tiene mucho peso gracias a HBM para aceleradores de IA.

La batalla tampoco va solo de rendimiento bruto. En memoria pesan muchísimo la densidad, el coste por bit, la eficiencia energética, la fiabilidad a largo plazo y la facilidad para escalar producción. Una arquitectura técnicamente brillante puede quedarse fuera si exige demasiados pasos, demasiada litografía avanzada o un rendimiento de fabricación insuficiente.

IA, HBM y DRAM empujan el cambio de arquitectura

El auge de la IA está acelerando una transición que probablemente habría llegado de todos modos. La demanda de memoria de alto ancho de banda, servidores densos y aceleradores especializados ha convertido la DRAM avanzada en un recurso estratégico. Ya no se trata solo de fabricar módulos para PC o móviles, sino de alimentar infraestructuras completas de computación.

Por eso, los enfoques de Samsung y SK hynix deben leerse como parte de una carrera mucho más amplia. La industria necesita memorias con más capacidad por chip, menor consumo por bit, mejor escalabilidad y mayor rendimiento sostenido. El salto hacia estructuras más complejas, ya sea mediante GAAFET, 4F² o futuras variantes de 3D DRAM, responde directamente a esa presión.

Por ahora, ninguna de las dos vías puede darse por ganadora. Lo importante es que ambas compañías parecen intentar resolver el mismo cuello de botella desde ángulos distintos. Si una de estas arquitecturas termina convirtiéndose en modelo dominante, podría definir buena parte de la próxima década de DRAM para IA, servidores y dispositivos de alto rendimiento.

Vía: Wccftech