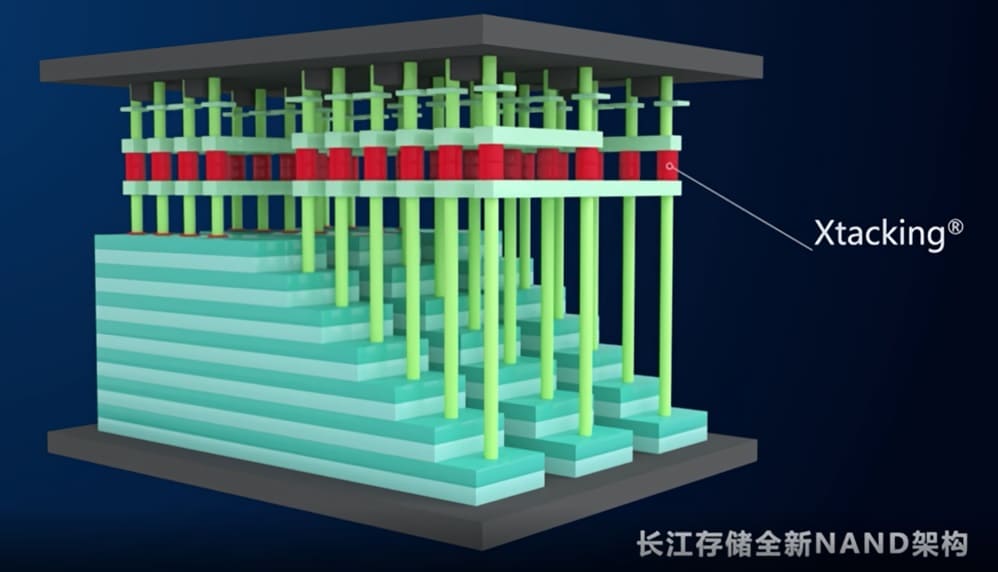

El fabricante de memorias chino YMTC (Yangtze Memory Technology Corp) supuestamente está desarrollando su propia arquitectura 3D NAND flash Xtacking 4.0 para la próxima generación de chips de memoria.

Según la documentación obtenida por Tom’s Hardware, YMTC habría desarrollado dos modelos basados en el renovado Xtacking 4.0: X4-9060, una 3D NAND de 128 capas y tres bits por celda (TLC), y X4-9070, una 3D NAND de 232 capas TLC.

Al hacer uso del apilamiento en cadena en ambos modelos, YMTC tiene previsto que la 3D NAND funcione incorporando matrices con 64 y 116 capas activas apiladas unas sobre otras. De este modo, se cumplirán las normas de exportación del gobierno estadounidense y la compañía podrá utilizar las herramientas que no figuran en el listado de sanciones.

Pese a que YMTC aún no ha dado a conocer todas las ventajas específicas de la tecnología Xtacking 4.0, el sector prevé mejoras significativas en la velocidad de transferencia de datos y la densidad de almacenamiento.

Se espera que estas mejoras se deriven del mayor número de planos para optimizar el procesamiento paralelo, el perfeccionamiento de las configuraciones de las líneas de bits dirigidas a minimizar la latencia y el desarrollo de variantes de chip modificadas para incrementar el rendimiento de la producción.

En el momento en que YMTC anunció Xtacking 3.0, la firma ofrecía variantes de 128 capas TLC y 232 capas de cuatro bits por celda (QLC) y se erigió como la primera compañía en alcanzar un recuento de más de 200 capas en el espacio 3D NAND.

La arquitectura Xtacking 3.0 incorpora técnicas de apilamiento de cadenas e interconexión híbrida y utiliza un nodo de proceso maduro para la capa inferior CMOS del chip. Tendremos que esperar a conocer los detalles definitivos de Xtacking 4.0 en el momento en que YMTC los lance oficialmente al mercado.

Vía: TechPowerUp