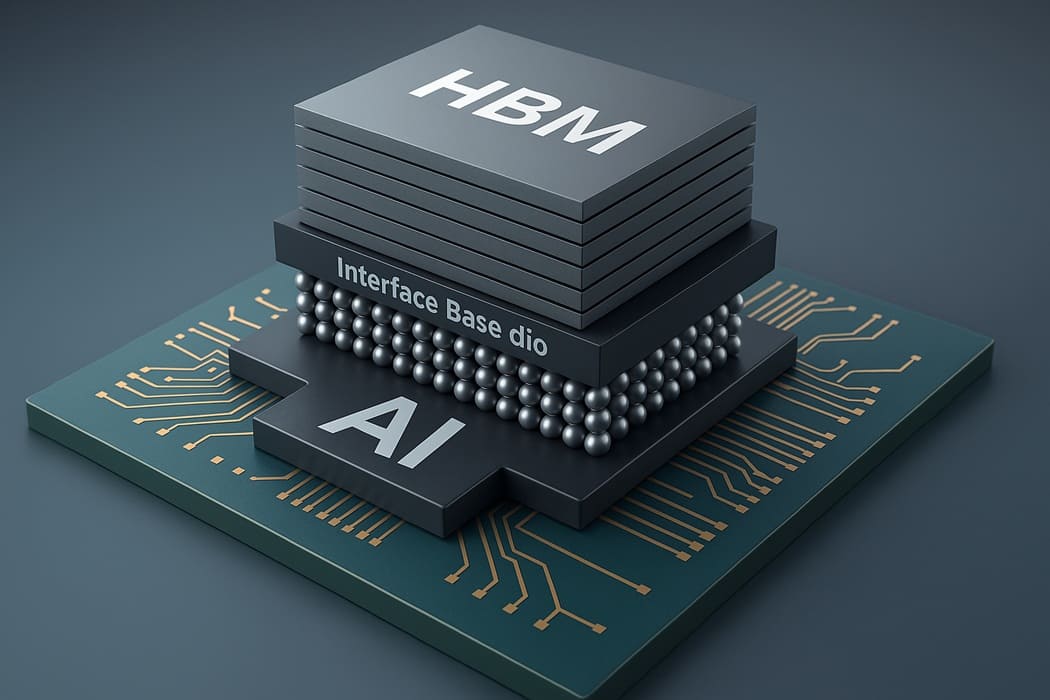

El sector de memoria avanzada se prepara para la llegada del nuevo estándar SPHBM4, una propuesta que JEDEC está ultimando y que redefine el diseño de memoria de alto ancho de banda empleada en aceleradores de IA. El estándar conserva los dies DRAM de HBM4, pero introduce una interfaz completamente rediseñada, pensada para operar sobre sustratos orgánicos y reducir el coste estructural de integrar grandes pilas de memoria en sistemas complejos.

El objetivo es claro: ofrecer un módulo con el mismo rendimiento agregado que HBM4, pero con una arquitectura de señalización más simple, menor densidad de pines y una mayor flexibilidad en la construcción de sistemas de gran capacidad, cruciales para modelos de IA generativa, entrenamiento multimodal y procesamiento intensivo en centros de datos.

SPHBM4 reduce a 512 señales gracias a la serialización 4:1 manteniendo el ancho de banda de HBM4

El diseño original de HBM4 requiere 2.048 señales de datos, un valor extremamente alto que obliga al uso de interposers de silicio y limita la escalabilidad física del módulo. El nuevo estándar SPHBM4, en cambio, define 512 señales, emplea serialización 4:1 y opera a frecuencias más elevadas para igualar el ancho de banda total previsto para la generación HBM4.

Este cambio permite lograr un paso de bump más relajado, condición imprescindible para montar las pilas de memoria sobre sustratos orgánicos, que son más económicos, más fáciles de manufacturar y admiten mayor libertad en la distribución térmica. La reducción del pinout también simplifica el diseño de SoC para IA, que ya no necesitan integrar miles de pads de alta densidad para acceder a toda la memoria.

Misma capacidad por pila que HBM4 con la ventaja adicional de canales más largos desde el SoC

SPHBM4 utiliza exactamente los mismos núcleos DRAM apilados que HBM4, por lo que la capacidad máxima por pila se mantiene sin cambios, permitiendo configuraciones de memoria equivalentes en aplicaciones de IA, HPC y análisis masivo de datos. La diferencia clave está en el ruteo: los sustratos orgánicos permiten canales más largos desde el SoC hasta la pila de memoria, lo que a su vez posibilita aumentar el número total de pilas SPHBM en un mismo sistema.

Esto abre la puerta a procesadores con más capacidad total de memoria, un aspecto crítico para modelos multimodales que manejan contextos más amplios, mayores volúmenes de parámetros y necesitan flujos de datos continuos sin saturar el bus. A medida que crece el tamaño de los modelos y el volumen de inferencias simultáneas, esta capacidad adicional se convierte en un elemento estratégico para competidores del sector.

Un estándar próximo a completarse y orientado a las necesidades del mercado de IA

El estándar SPHBM4 está en su fase final de definición dentro de JEDEC, con ajustes posibles antes de su publicación oficial, pero con una arquitectura ya consolidada: 512 señales, serialización 4:1, interfaz optimizada para altas frecuencias, compatibilidad con sustratos orgánicos y equivalencia total en capacidad respecto a HBM4. El desarrollo refleja una tendencia clara en el mercado: reducir el coste y la complejidad del empaquetado sin renunciar al rendimiento extremo.

Para los fabricantes de aceleradores de IA, SPHBM4 supone un camino intermedio entre las soluciones de memoria avanzada basadas en silicio y las nuevas generaciones de módulos orientados a ancho de banda masivo, permitiendo construir plataformas con mayor capacidad, menor coste térmico y más libertad de diseño. La estandarización será clave para impulsar la adopción en centros de datos, infraestructuras de inferencia y futuros SoC con IA integrada.

Vía: TechPowerUp