CXL Consortium ha publicado la nueva especificación Compute Express Link 4.0, una evolución clave para los centros de datos que manejan cargas de trabajo de IA y HPC cada vez más exigentes. La actualización duplica la velocidad de transferencia respecto a CXL 3.1, amplía la compatibilidad con aceleradores heterogéneos y refuerza la estabilidad del ecosistema de memoria coherente que sustenta la computación moderna.

Ancho de banda de 128 GT/s y cero latencia añadida

El salto principal de CXL 4.0 reside en el incremento del ancho de banda hasta 128 GT/s, el doble que la generación anterior, manteniendo latencia nula adicional. Esta mejora directa en la interconexión de memoria y cómputo permite mover datos con mayor rapidez entre dispositivos CXL, beneficiando tareas de inferencia, análisis de datos o entrenamiento de modelos multimodales.

La especificación conserva las optimizaciones de CXL 3.x, incluido el formato Flit 256 B, e introduce el concepto de anchura x2 nativa, pensado para aumentar el fan-out en arquitecturas con múltiples aceleradores. Este enfoque busca que las futuras plataformas escalen sin cuellos de botella de comunicación interna.

Más alcance físico y nuevas funciones de puerto combinado

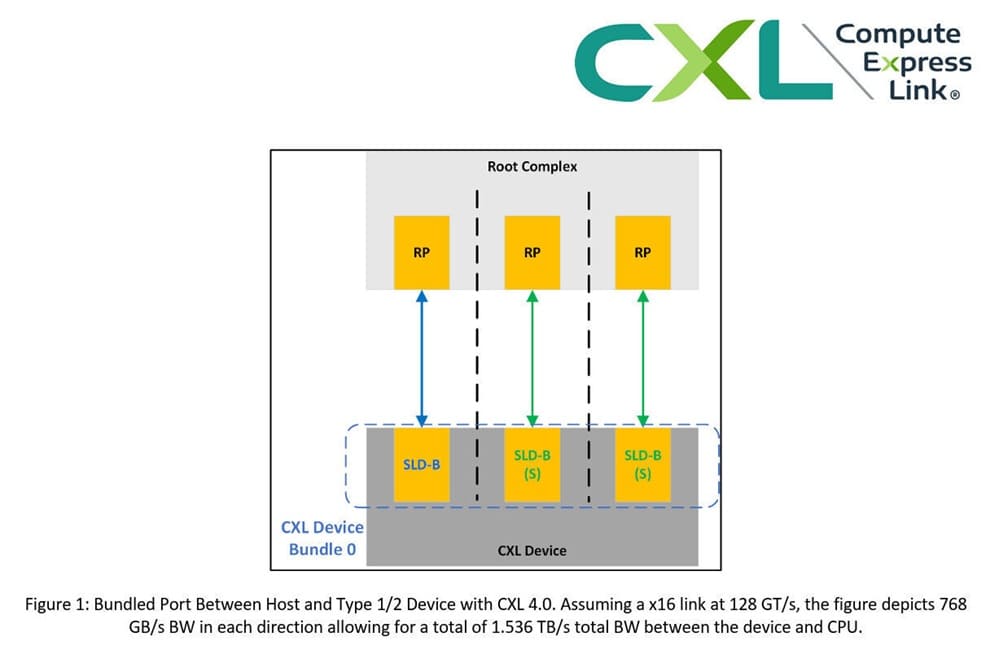

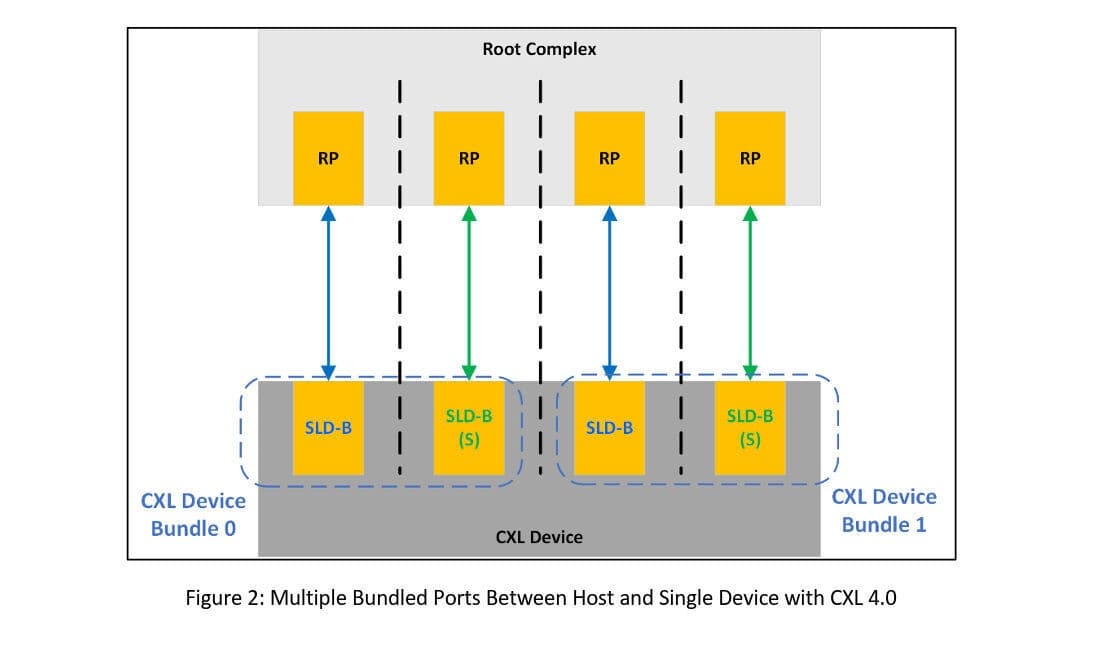

Entre las novedades físicas destaca el soporte para hasta cuatro retimers, lo que amplía el alcance del canal y la calidad de señal en sistemas de gran densidad. También se implementan capacidades de puerto combinado CXL, que permiten unir enlaces entre el host y dispositivos tipo 1 y 2 (aceleradores CXL) para incrementar el ancho de banda efectivo de la conexión.

Estas mejoras consolidan a CXL 4.0 como el estándar de referencia en interconexiones coherentes, especialmente en configuraciones con múltiples GPU, NPU y controladores de memoria distribuida, donde la eficiencia de enlace es crítica para el rendimiento agregado.

Fiabilidad, mantenimiento y compatibilidad total

En el apartado de fiabilidad y mantenimiento, la versión 4.0 refuerza las capacidades RAS (Reliability, Availability and Serviceability), mejorando la visibilidad de errores y la eficiencia en tareas de diagnóstico preventivo. El objetivo es reducir tiempos de parada en clústeres de producción y facilitar el mantenimiento predictivo mediante herramientas unificadas.

La especificación mantiene compatibilidad total con CXL 3.x, 2.0, 1.1 y 1.0, una prioridad para fabricantes de placas base y módulos de memoria que ya implementan hardware basado en generaciones anteriores. Esto garantiza una transición fluida entre plataformas sin necesidad de rediseños complejos.

Adopción y próximos pasos en el ecosistema CXL

El anuncio de CXL 4.0 coincide con la preparación del evento Supercomputing 2025 (SC’25), donde se mostrarán demostraciones prácticas en el CXL Pavilion (stand 817). La organización también celebrará un seminario técnico el 4 de diciembre para profundizar en las novedades de la norma y orientar a desarrolladores sobre su implementación.

Con este avance, CXL Consortium, respaldado por compañías como NVIDIA, Intel, AMD y Samsung, consolida la hoja de ruta hacia un futuro de memoria unificada, coherente y escalable que sirva tanto al sector de IA como al sector de semiconductores de nueva generación.

Vía: TechPowerUp