En su presentación de la ISSCC 2023, AMD detalló cómo ha avanzado en la eficiencia energética de los centros de datos y cómo ha conseguido seguir el ritmo de la Ley de Moore, incluso cuando los avances en los nodos de las fundiciones de semiconductores han disminuido.

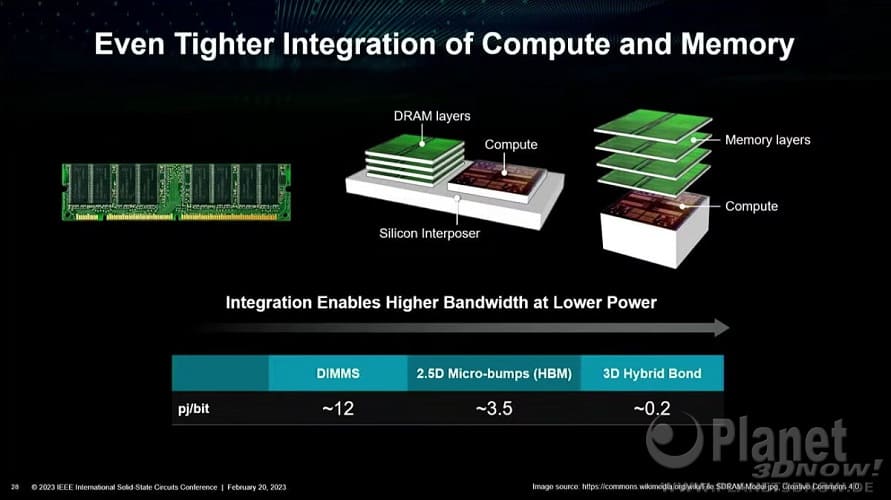

Quizá su predicción más llamativa para los procesadores de servidor y los aceleradores HPC sea la DRAM apilada multicapa. Desde hace algún tiempo, la compañía fabrica productos lógicos, como GPUs con HBM apilada. Se trata de módulos multichip (MCM), en los que el chip lógico y las pilas de HBM se colocan sobre un intercalador de silicio.

Aunque esto ahorra espacio en el PCB en comparación con los chips/módulos de memoria discretos, resulta ineficaz en el sustrato, y el intercalador es esencialmente un die de silicio que posee un cableado microscópico entre los chips apilados sobre él.

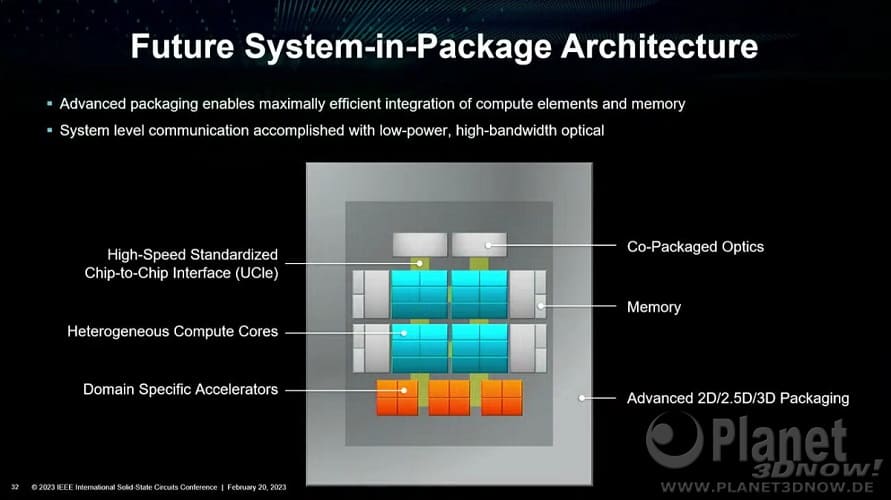

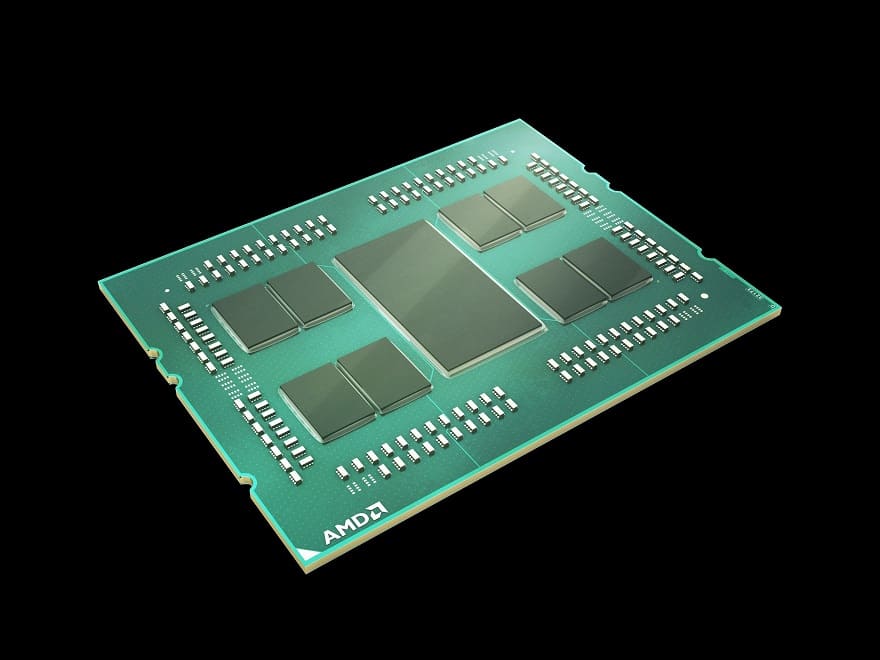

AMD prevé que el procesador de servidor de alta densidad del futuro cercano disponga de múltiples capas de DRAM apiladas sobre chips lógicos. Este método de apilamiento ahorraría espacio en el PCB y el sustrato, lo que permitiría a los diseñadores de chips incorporar aún más núcleos y memoria por socket.

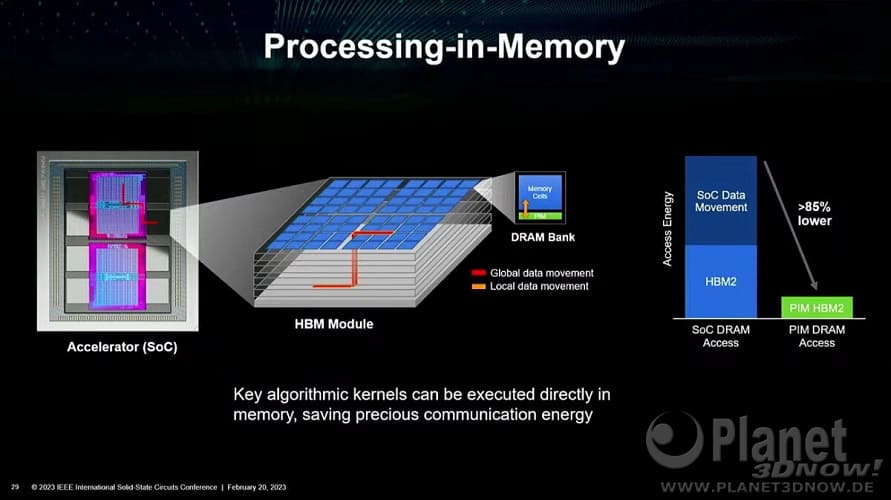

La compañía también contempla un mayor protagonismo de la computación en memoria, donde las funciones triviales de cálculo simple y movimiento de datos pueden ejecutarse directamente en la memoria, ahorrando desplazamientos de ida y vuelta al procesador.

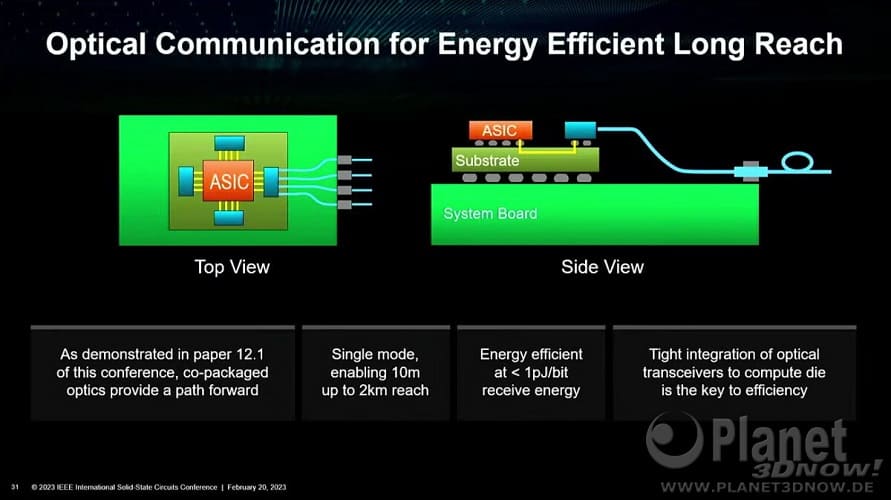

Por último, la compañía también habló sobre la posibilidad de un PHY óptico en el propio pack, que simplificaría la infraestructura de red.

Vía: TechPowerUp