AMD ha anunciado oficialmente la nueva familia Kintex UltraScale+ Gen 2, una actualización estratégica dentro del segmento intermedio de FPGA, orientada a mercados que priorizan fiabilidad, estabilidad de plataforma y ciclos de vida muy prolongados. El lanzamiento apunta directamente a sectores como imagen médica, automatización industrial y producción de vídeo profesional, donde la longevidad del hardware es tan importante como el rendimiento.

Lejos de tratarse de una simple reducción litográfica, los Kintex Gen 2 representan una modernización arquitectónica profunda sobre la plataforma Kintex UltraScale+ de 16 nm, incorporando nuevos estándares de memoria, conectividad de alta velocidad y mejoras de seguridad pensadas para las cargas de trabajo intensivas en datos que dominarán hasta la fecha y más allá de 2027.

Evolución de una plataforma ampliamente adoptada

La familia Kintex UltraScale+, heredada de la etapa de Xilinx, se ha consolidado durante años como una solución equilibrada en rendimiento por vatio, encontrando su lugar en aplicaciones tan diversas como equipos de ultrasonidos, infraestructura 5G o sistemas de procesamiento en el borde.

Sin embargo, el crecimiento de las demandas de ancho de banda y movimiento de datos en dispositivos edge empezó a dejar obsoletas las opciones de conectividad de la primera generación. La actualización Gen 2 responde directamente a esta necesidad, con una clara prioridad en la modernización del subsistema de entrada y salida, sin romper la compatibilidad de ecosistema que valoran los clientes industriales.

Nuevo subsistema de memoria y conectividad avanzada

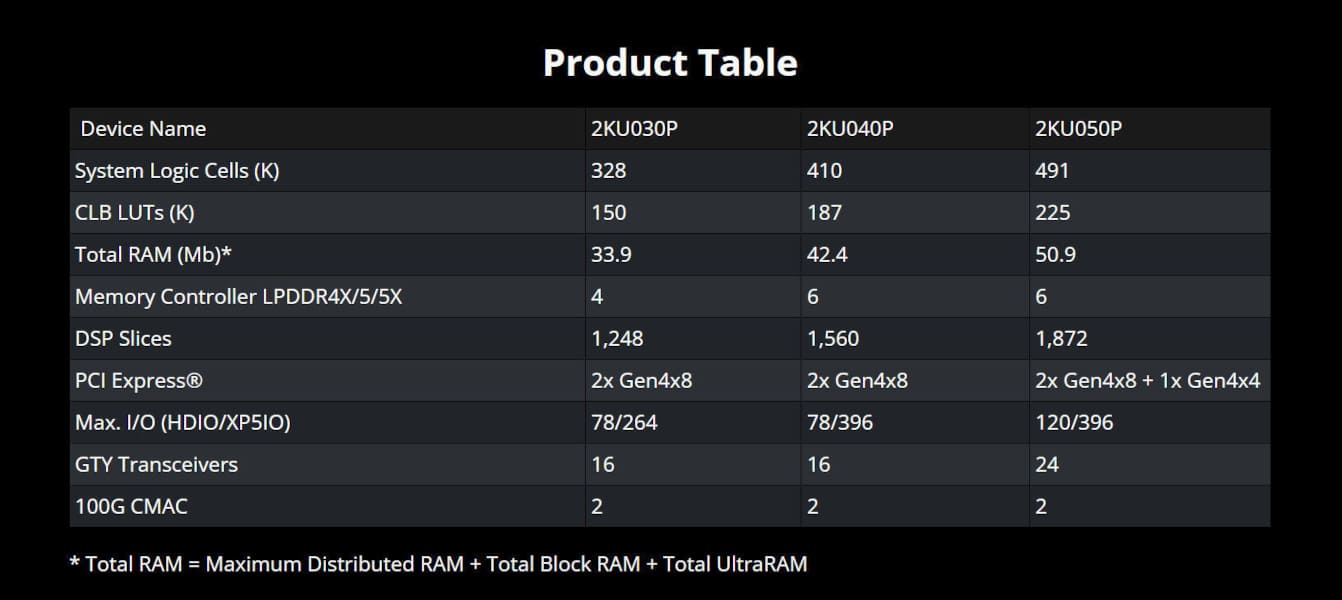

Uno de los cambios más relevantes en los Kintex UltraScale+ Gen 2 es la renovación completa del subsistema de memoria. AMD abandona DDR4 y adopta LPDDR4X, DDR5 y LPDDR5X, permitiendo mayores anchos de banda, mejor eficiencia energética y compatibilidad con diseños compactos.

Las memorias LPDDR resultan especialmente atractivas en entornos de IIoT (Internet industrial de las cosas) y sistemas embebidos de bajo consumo, abriendo además la puerta a una nueva generación de cámaras 4K y 8K de nivel broadcast, donde las FPGA siguen siendo preferidas frente a ASIC o SoC complejos por sus volúmenes de producción reducidos y flexibilidad.

En conectividad, AMD introduce PCI-Express Gen 4, un salto importante frente a Gen 3, junto a bloques MAC Ethernet duales de 100 Gb, claves para aplicaciones industriales que requieren agregación de datos en tiempo real y baja latencia.

Estrategia frente a Intel y Lattice

Con esta familia, AMD compite directamente con soluciones como Intel Agilex 5 y la serie Avant de Lattice Semiconductor. Mientras Intel emplea su nodo Intel 7 y Lattice se apoya en TSMC de 16 nm FinFET, AMD ha optado deliberadamente por mantener el nodo de 16 nm ya utilizado en la generación anterior.

Esta decisión refleja una apuesta clara por la estabilidad de plataforma, la reducción de costes NRE (Non-Recurring Engineering) y la seguridad de suministro, factores críticos para clientes industriales y gubernamentales. A cambio, AMD ofrece mejoras en rendimiento, frecuencia máxima, conectividad y lógica LUT6, frente a las LUT4 utilizadas por algunos competidores, sin obligar a rediseños drásticos.

Seguridad integrada para entornos críticos

La seguridad ocupa un papel central en los Kintex UltraScale+ Gen 2. AMD ha integrado criptografía de nivel CNSA 2.0, cifrado de bitstream y protecciones anti-clonado directamente en el silicio, abordando uno de los mayores riesgos de las FPGA: la protección de la propiedad intelectual.

Estas capacidades permiten desplegar los chips en entornos zero-trust, garantizando arranque autenticado y operaciones seguras incluso en infraestructuras críticas donde la exposición física del hardware es una posibilidad real.

Disponibilidad a largo plazo y calendario

AMD se ha comprometido a mantener la familia Kintex UltraScale+ Gen 2 disponible hasta 2045, un horizonte que resulta especialmente atractivo para sectores como aeroespacial y defensa, donde los ciclos de vida de los sistemas pueden extenderse durante décadas.

En cuanto al calendario, el soporte para Vivado y Vitis llegará en Q3 de 2026, con las primeras muestras de ingeniería previstas para Q4 de 2026. La producción en volumen arrancará durante la primera mitad de 2027, marcando el inicio de una nueva etapa para una de las plataformas FPGA más longevas del sector.

Vía: TechPowerUp