La carrera por escalar la memoria en IA sigue acelerándose, y ahora con una pista directa desde el propio diseño de hardware. OpenAI ha registrado una patente que describe un chip con múltiples chiplets de cómputo rodeados por numerosos stacks de HBM, conectados mediante puentes lógicos embebidos. Más allá del concepto, lo relevante es lo que intenta resolver: los límites físicos actuales del empaquetado de memoria de alto ancho de banda.

Este planteamiento no es menor. El acceso a grandes cantidades de memoria es uno de los principales cuellos de botella en IA, y cualquier avance en este punto tiene impacto directo en el tamaño y eficiencia de los modelos.

El límite actual: HBM pegada al chip y con distancia crítica

Hoy en día, la integración de HBM está condicionada por normas físicas muy estrictas. El estándar JEDEC obliga a colocar la memoria cerca del chip principal, con interconexiones metálicas que no suelen superar los 6 mm de distancia.

Este límite no es arbitrario. A mayor distancia, mayor latencia y pérdida de señal, lo que reduce el rendimiento global. Por eso, los diseños actuales suelen quedarse en configuraciones de 4, 6 u 8 stacks de HBM, un techo que condiciona la capacidad total disponible.

Desde una lectura analítica, este es uno de los grandes frenos actuales. No es que no se pueda añadir más memoria, es que no se puede hacer sin penalizar el rendimiento, y eso limita directamente la escalabilidad de los chips de IA.

Embedded Logic Bridges: la clave para romper el límite físico

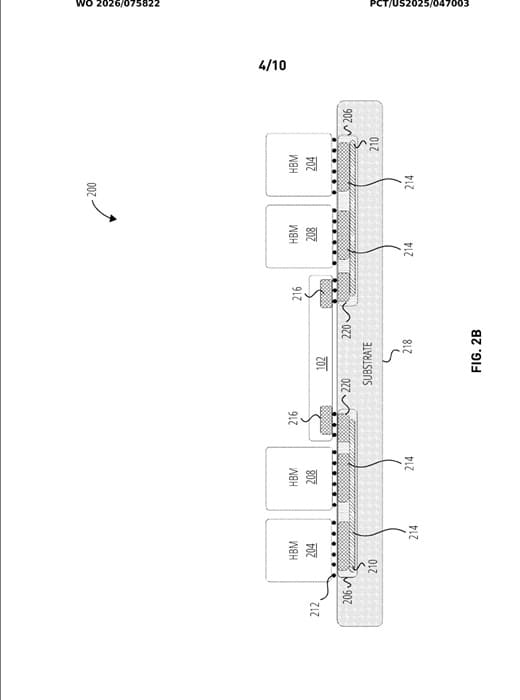

La propuesta de OpenAI introduce un elemento clave: puentes lógicos embebidos capaces de extender la distancia efectiva hasta unos 16 mm, más del doble del límite actual.

Esto cambia completamente el diseño. Permite separar físicamente los stacks de HBM sin perder eficiencia en la comunicación, algo fundamental para escalar el número de módulos.

Además, estos puentes no son simples conexiones. Pueden actuar como controladores de memoria o como interfaces PHY de alta velocidad, lo que añade inteligencia al propio interconectado.

Desde un punto de vista técnico, esto es importante. El interconectado deja de ser un simple canal pasivo y pasa a ser un elemento activo del sistema, mejorando la gestión de datos dentro del chip.

De 8 a 20 stacks de HBM: un salto en capacidad real

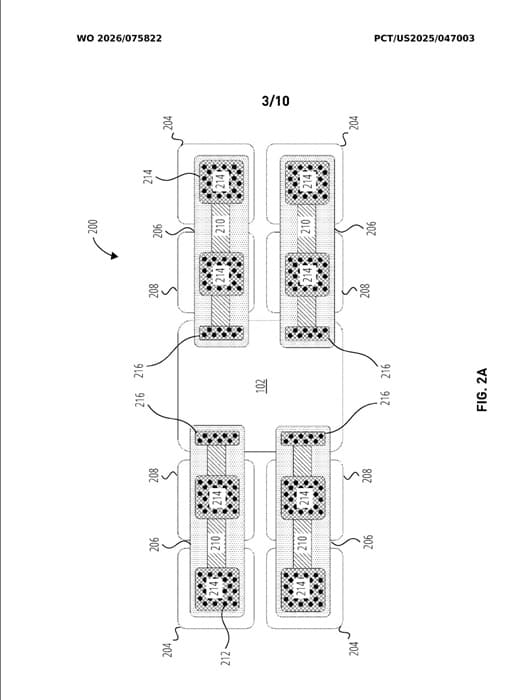

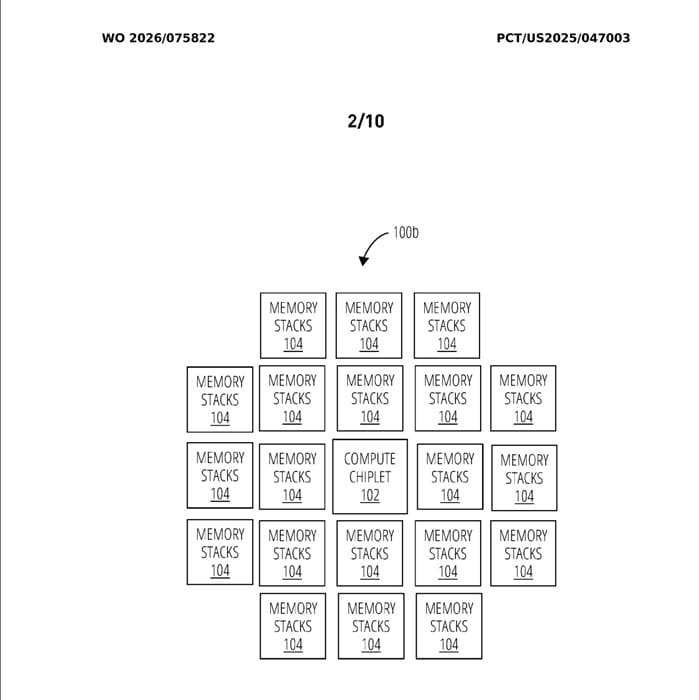

Uno de los ejemplos de la patente es especialmente revelador. OpenAI describe un diseño con hasta 20 stacks de HBM alrededor de un chiplet de cómputo, algo muy por encima de las configuraciones actuales.

Este salto tiene implicaciones directas. Más stacks significa más capacidad de memoria y mayor ancho de banda agregado, dos factores críticos para entrenar y ejecutar modelos de IA de gran tamaño.

Desde una lectura estratégica, esto apunta a un objetivo claro. Reducir la dependencia de memoria externa y acercar el máximo volumen de datos al propio chip, mejorando eficiencia energética y rendimiento.

UCIe y D2D: el estándar que hace viable el diseño

La arquitectura propuesta se apoya en interfaces D2D (die-to-die) compatibles con el estándar UCIe, que está ganando protagonismo como base para sistemas modulares de chiplets.

Este punto es clave porque no es una solución propietaria cerrada, sino alineada con estándares de la industria. Esto aumenta su viabilidad real, ya que facilita la interoperabilidad entre distintos bloques y fabricantes.

Desde el análisis de mercado, esto refuerza una tendencia clara. El futuro del chip no es monolítico, es modular, y los chiplets conectados de forma eficiente son el camino dominante.

Paralelismo con Intel EMIB: tecnología existente con enfoque similar

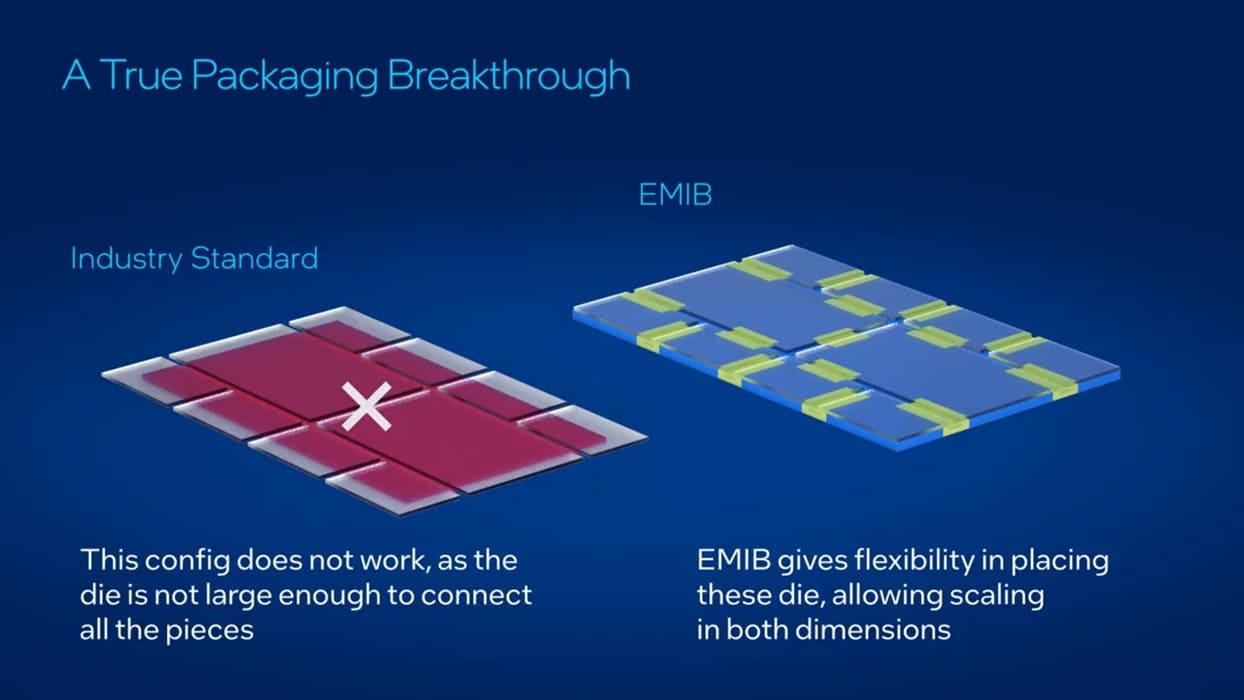

La idea no surge en el vacío. Soluciones como EMIB de Intel ya trabajan en un enfoque similar, utilizando puentes para conectar chiplets sin necesidad de grandes interposers.

EMIB permite superar límites físicos tradicionales, reducir costes y mejorar flexibilidad de diseño, características que encajan directamente con lo planteado por OpenAI.

Esto abre una posibilidad interesante. No es descartable que diseños futuros combinen ideas como las de esta patente con tecnologías ya existentes, acelerando su llegada al mercado.

Lectura estratégica: la memoria se convierte en el verdadero centro del chip de IA

El punto más importante no es la patente en sí, sino lo que representa. El foco del diseño de chips de IA está desplazándose hacia la memoria, no solo hacia la potencia de cálculo.

Aumentar el número de stacks de HBM implica algo más profundo. Permite alimentar modelos más grandes sin depender de arquitecturas distribuidas complejas, reduciendo latencias y mejorando eficiencia.

En este contexto, la propuesta de OpenAI deja una idea clara. El futuro del rendimiento en IA no depende solo de más núcleos, sino de cómo se organiza y accede a la memoria, y ahí es donde se está librando la verdadera batalla tecnológica.

Vía: Wccftech