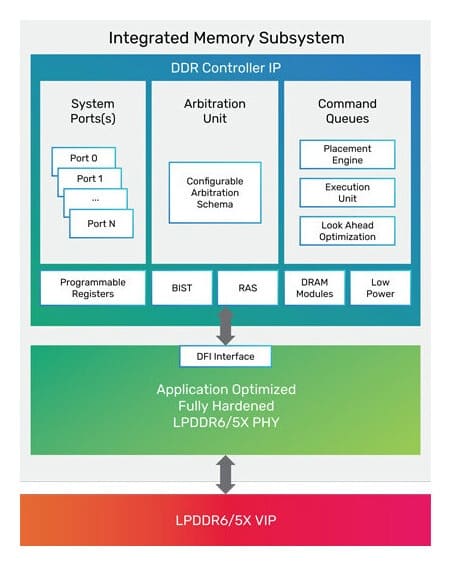

Cadence ha anunciado la primera solución de sistema IP de memoria LPDDR5X a 9.600 Mbps diseñada específicamente para entornos empresariales y centros de datos, un terreno donde hasta ahora este tipo de memoria encontraba barreras claras en términos de fiabilidad y RAS. La clave del avance está en la integración del IP LPDDR5X ya validado en producción de Cadence con el esquema ECC RAIDDR desarrollado por Microsoft, que debuta aquí como primer cliente de la solución.

El objetivo es romper el compromiso tradicional entre eficiencia energética, rendimiento y fiabilidad, acercando LPDDR5X al nivel de robustez que históricamente ha caracterizado a DDR5 en centros de datos.

LPDDR5X gana peso en IA, pero con límites claros hasta ahora

En la expansión actual de la infraestructura de IA, la memoria LPDDR5X está ganando protagonismo gracias a su menor consumo y a su capacidad para reducir latencias y tiempos de ejecución en IA, HPC y otras cargas intensivas en memoria. Sin embargo, los hiperescaladores se han encontrado con un dilema persistente: LPDDR5X ofrece una excelente relación PPA (potencia, rendimiento y área), pero carece de las garantías RAS que aporta DDR5 con ECC tradicional.

La nueva solución de Cadence aborda directamente ese problema, ofreciendo capacidades RAS de nivel empresarial sin sacrificar la densidad ni la eficiencia energética que hacen atractiva a LPDDR5X.

ECC RAIDDR: fiabilidad DDR5 en memoria LPDDR

En el núcleo del sistema se encuentra RAIDDR, el algoritmo de corrección de errores ECC de nueva generación de Microsoft. Este esquema logra una protección cercana a la corrección de datos de dispositivo único (SDDC), con una precisión de detección de fallos líder en la industria y un sobrecoste lógico mínimo.

RAIDDR ofrece una protección equivalente al ECC basado en símbolos utilizado tradicionalmente en DDR5 RDIMM, algo especialmente relevante para centros de datos. Además, la implementación emplea ECC por canal lateral (sideband ECC), lo que permite mantener el ancho de banda completo del canal de memoria, evitando penalizaciones de rendimiento.

Rendimiento de 9.600 Mbps en un formato compacto

Basada en tecnología DRAM LPDDR5X, la solución alcanza velocidades de hasta 9.600 Mbps, manteniendo un formato compacto, ideal para sistemas con restricciones de espacio, como aceleradores de IA o plataformas densamente integradas.

Entre sus características técnicas más relevantes se incluyen:

- Canales de 40 bits con DRAM LPDDR5X

- 9.600 Mbps combinados con bajo consumo energético

- Fiabilidad RAS de nivel empresarial, comparable a DDR5 con ECC por símbolos

- ECC sideband para maximizar el ancho de banda efectivo

- Alta densidad y optimización PPA para centros de datos

Este enfoque permite integrar memoria eficiente y fiable en arquitecturas donde cada vatio y cada milímetro cuadrado cuentan.

Un paso clave para la memoria en centros de datos

La disponibilidad de esta solución como subsistema completo de IP la hace especialmente atractiva para entrenamiento e inferencia de IA, donde la eficiencia energética es ya tan crítica como el rendimiento bruto. Además, encaja dentro de la hoja de ruta de Cadence hacia memorias de próxima generación: en julio de 2025, la compañía ya presentó su solución LPDDR6 a 14,4 Gbps, reforzando su apuesta por escalar rendimiento sin disparar el consumo.

Con esta propuesta, Cadence amplía un portafolio que ya cubre LPDDR, HBM, DDR5, PCIe, UCIe, UALink y Ethernet de alta velocidad, con IP probada en silicio y soporte para chiplets y 3D-ICs.

LPDDR5X entra en la liga “enterprise”

La combinación de LPDDR5X a 9.600 Mbps con ECC RAIDDR marca un punto de inflexión: por primera vez, esta memoria puede cumplir exigencias de fiabilidad propias de centros de datos, sin renunciar a su ventaja energética. Si la adopción por parte de Microsoft se consolida, el movimiento podría acelerar un cambio estructural en cómo se diseñan los subsistemas de memoria para IA y HPC en los próximos años.

Vía: TechPowerUp