Intel ha mejorado la fiabilidad del software mediante la creación de mejoras de silicio realizadas a través de la lógica dentro del procesador. La compañía ha presentado hoy una nueva técnica para complementar las mitigaciones de software existentes para los ataques de inyección de fallos.

El Circuito de Réplica Sintonizable (TRC, por sus siglas en inglés) – Protección contra la Inyección de Fallos utiliza sensores basados en hardware para detectar específicamente los fallos de sincronización basados en el circuito que se producen como resultado de un ataque. TRC se integra por primera vez en la familia de procesadores Intel Core de 12ª Generación y añade la tecnología de detección de inyección de fallos al Motor de Seguridad y Gestión Convergente Intel (Intel CSME), diseñada para detectar ataques de error físicos no invasivos en los pins que suministran el reloj y el voltaje. El TRC también está diseñado para detectar inyecciones de fallos electromagnéticos.

«Las protecciones del software se han reforzado con la virtualización, los diferentes stacks (canaries) y la autenticación del código antes de su ejecución», resalta Daniel Nemiroff, senior principal engineer de Intel. «Esto ha llevado a actores malintencionados a centrar su atención en atacar físicamente las plataformas informáticas. Una de las herramientas favoritas de estos atacantes son los ataques de inyección de fallos a través del voltaje, las clavijas de reloj y la radiación electromagnética que provocan fallos de sincronización de los circuitos y pueden permitir la ejecución de instrucciones maliciosas y la posible exfiltración de secretos».

El TRC fue desarrollado originalmente por los laboratorios de Intel para supervisar las variaciones dinámicas, como la caída de tensión, la temperatura y el envejecimiento de los circuitos, con el fin de mejorar el rendimiento y la eficiencia energética. De este modo, a medida que las nuevas tecnologías evolucionan, también lo hacen sus aplicaciones.

«Cambiando la configuración de la monitorización y construyendo la infraestructura para aprovechar la sensibilidad del TRC a los ataques de inyección de fallos, el circuito se ajustó a las aplicaciones de seguridad», indicó Carlos Tokunaga, principal engineer de Intel Labs, para explicar el enfoque de la investigación.

Para ello, Intel Labs, iSTARE--PASCAL (Physical Attack and Side Channel Analysis Lab) y el Grupo de Computación de Clientes (Client Computing Group) de Intel se asociaron para probar y validar el TRC para escenarios de seguridad. Juntos demostraron que el TRC puede calibrarse hasta un punto en el que esas violaciones de la sincronización sólo podrían ser el resultado de un ataque. Por ello, Intel aplicó el TRC como un sensor de hardware para detectar y proteger contra estos métodos de ataque de inyección de fallos.

El TRC está diseñado para proteger contra ciertos tipos de ataques físicos mediante la supervisión del retraso de tipos específicos de circuitos digitales. Cuando se calibra según las expectativas específicas de la sensibilidad del sensor, el TRC señala un error cuando detecta un fallo de sincronización debido a un voltaje, reloj, temperatura o fallo electromagnético. Dado que el TRC está calibrado para señalar un error a un nivel de tensión más allá del rango de funcionamiento nominal del CSME, cualquier condición de error del TRC es una indicación de que los datos podrían estar corruptos, lo que desencadena técnicas de mitigación para garantizar su integridad.

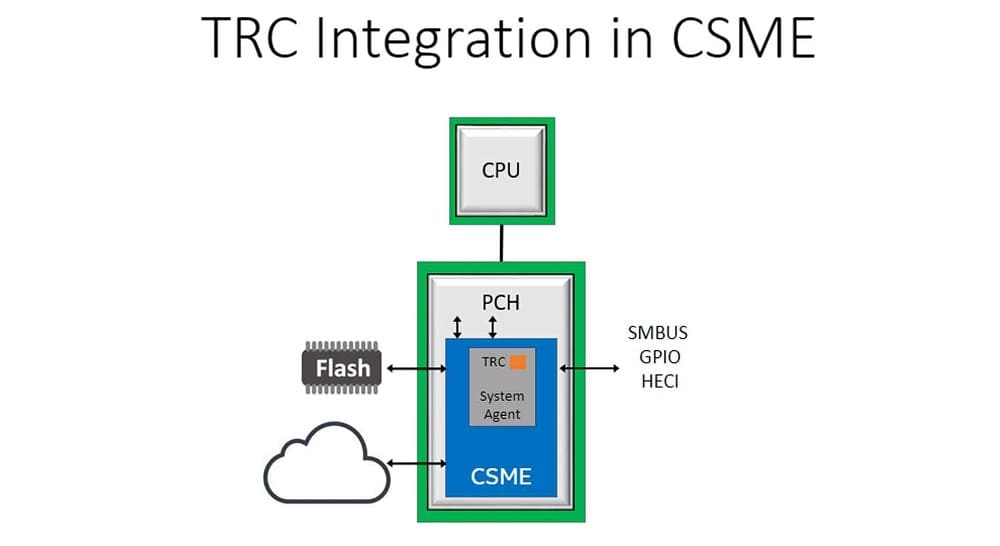

Intel ha aplicado el TRC al Platform Controller Hub (PCH), un chipset separado y aislado de la CPU que mejora la protección de la raíz de confianza de un sistema llamado Intel CSME.

El aspecto más crucial para producir este tipo de sensor de hardware es la calibración. Si se calibra de forma demasiado agresiva, el sensor detectaría caídas de tensión normales de la carga de trabajo como falsos positivos. Los falsos positivos crean ruido y podrían provocar la inestabilidad de la plataforma, lo que supondría una carga adicional para los equipos de ciberseguridad que ya están sobrecargados.

Para evitar los falsos positivos, Intel desarrolló un flujo de calibración basado en la retroalimentación. También es importante minimizar los falsos negativos, por lo que el bucle de retroalimentación utiliza los resultados de las pruebas de falsos positivos y falsos negativos junto con los datos de margen del sensor de hardware. Esto indica lo cerca que estuvo el sensor de detectar un fallo de seguridad, así como la precisión de las bandas de guarda.

Los avances en la arquitectura a menudo pueden dar lugar a una sobrecarga de ejecución considerablemente menor en comparación con las implementaciones solo de software, aunque los métodos de ataque físico han estado tradicionalmente fuera de los modelos de amenaza.

A medida que se vincula más computación al edge inteligente, Intel ha invertido en capacidades de seguridad de protección contra ataques físicos para mejorar la resistencia del software, ya que las cargas de trabajo se expanden y los modelos de amenazas evolucionan. La seguridad es una propiedad a nivel de sistema arraigada en el silicio. Todos los componentes del sistema, desde el software hasta el silicio, pueden ayudar a mantener la seguridad de los datos.

Los detalles de esta investigación se presentaron en Black Hat USA 2022: Fault-Injection Detection Circuits: Design, Calibration, Validation and Tuning