TSMC ha presentado un adelanto de su nodo A13 durante el North America Technology Symposium, pero el verdadero foco no está en el nodo en sí, sino en la decisión tecnológica que lo acompaña. La compañía ha optado por continuar con litografía Low-NA EUV, evitando de momento el salto a High-NA EUV, una elección que impacta directamente en el coste de fabricación, el ritmo de escalado y la competitividad dentro del sector de semiconductores.

Lejos de ser una decisión conservadora, el movimiento refleja una estrategia muy calculada: exprimir al máximo la infraestructura actual, mantener un capex contenido y seguir avanzando en densidad sin asumir el enorme coste que implica la nueva generación de herramientas.

Low-NA EUV: eficiencia frente a inversión masiva

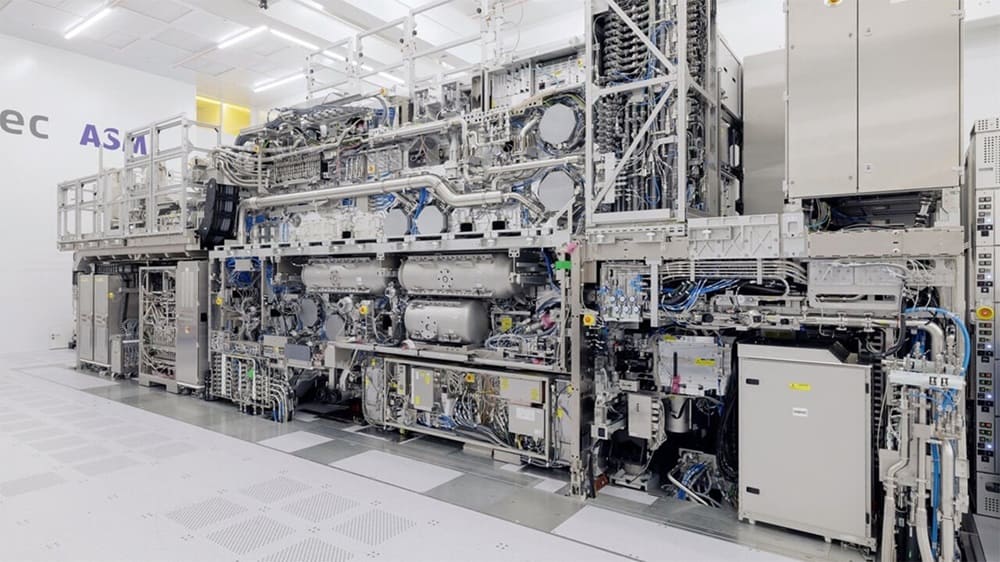

El punto crítico de esta decisión radica en el coste. Los sistemas High-NA EUV de ASML alcanzan cifras cercanas a los 350 millones de euros por unidad, lo que convierte cada ampliación de capacidad en una inversión colosal dentro de cualquier fabs de última generación.

Frente a esto, TSMC opta por Low-NA EUV, cuyo coste es aproximadamente la mitad, permitiendo mantener una estructura de inversión mucho más eficiente. Esta diferencia no solo afecta al gasto inicial, sino también al ritmo al que se pueden desplegar nuevas líneas de producción, algo crítico en un entorno donde la demanda de chips avanzados sigue creciendo impulsada por la IA, los centros de datos y el sector de GPU.

Según Kevin Zhang, la clave está en aprovechar al máximo la tecnología existente mientras se mantiene un roadmap agresivo, una combinación que permite a TSMC avanzar sin asumir riesgos financieros innecesarios.

Multi-patterning: la ingeniería detrás del enfoque de TSMC

Para compensar las limitaciones del Low-NA EUV, TSMC está recurriendo a técnicas avanzadas como el multi-patterning, un método que permite realizar múltiples exposiciones sobre una misma capa para mejorar la resolución final del proceso de grabado.

Este enfoque implica que una misma capa del chip puede ser procesada en varias pasadas, logrando así un nivel de precisión cercano al que ofrecería un sistema High-NA. En la práctica, esto permite a TSMC mantener densidades competitivas, optimizar el uso de su parque de maquinaria actual y evitar una transición prematura hacia tecnologías más costosas.

El resultado es una estrategia que prioriza la eficiencia operativa, manteniendo el equilibrio entre rendimiento del silicio, coste por oblea y capacidad de producción.

Un precedente que invita a la cautela

Este tipo de decisiones no es nuevo en la industria. Intel adoptó en su momento una estrategia similar durante el desarrollo de su nodo de 10 nm, intentando resolver los desafíos técnicos mediante multi-patterning con DUV antes de introducir EUV.

Aquella etapa estuvo marcada por retrasos y problemas de rendimiento, lo que obligó a la compañía a replantear su enfoque. Este precedente introduce un matiz importante: exprimir una tecnología existente puede ser eficiente, pero también arriesgado si se alcanzan sus límites demasiado pronto.

Intel acelera con High-NA EUV y toma la delantera

Mientras TSMC opta por maximizar el Low-NA EUV, Intel ha decidido avanzar en la dirección opuesta. La compañía ya lidera la integración de High-NA EUV, especialmente en su nodo 14A, donde esta tecnología permite un grabado más agresivo y preciso.

Este movimiento sitúa a Intel en una posición adelantada en cuanto a adopción de la nueva generación de litografía, aunque también implica asumir costes significativamente más elevados. La diferencia de enfoque entre ambas compañías refleja dos estrategias claras: eficiencia y optimización frente a adopción temprana y agresiva.

El tiempo determinará cuál de estas aproximaciones ofrece mejores resultados en términos de rendimiento, coste por transistor y escalabilidad futura.

El límite del Low-NA EUV ya está definido

A pesar de sus ventajas, el Low-NA EUV no es una solución indefinida. A medida que la industria se aproxima a nodos de 1 nm y por debajo, las limitaciones en resolución y precisión empiezan a ser más evidentes, incluso con técnicas avanzadas como el multi-patterning.

TSMC es consciente de este escenario y ya contempla la adopción de High-NA EUV en futuras generaciones. En ese punto, la transición será inevitable para mantener la competitividad en densidad y rendimiento dentro del sector de semiconductores.

Estrategia a corto plazo sólida, desafío a largo plazo

La apuesta actual de TSMC refuerza su posición a corto y medio plazo, permitiéndole mantener costes controlados, optimizar su infraestructura y seguir siendo competitiva frente a otros actores del mercado. Sin embargo, también deja claro que esta estrategia tiene un horizonte definido.

El equilibrio entre capex, madurez tecnológica y exigencias del mercado será clave en los próximos años. Por ahora, TSMC demuestra que todavía se puede exprimir el Low-NA EUV, pero el salto al High-NA ya no es una cuestión de si ocurrirá, sino de cuándo.

Vía: TechPowerUp