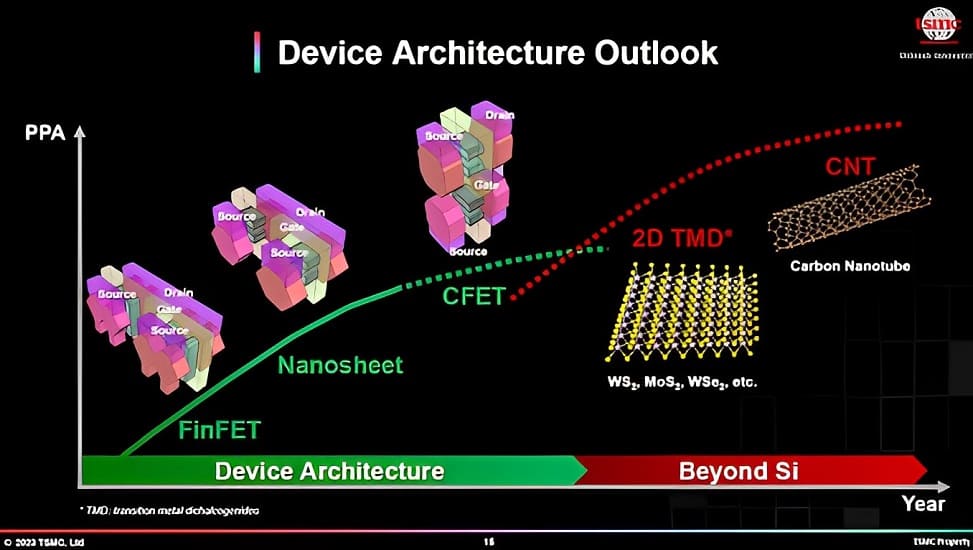

Durante el European Technology Symposium 2023, TSMC presentó detalles adicionales sobre la próxima tecnología FET complementaria (CFET) que impulsará la próxima generación de dispositivos basados en silicio. Con Nanosheet reemplazando a FinFET, la tecnología CFET hará lo propio con los nodos Gate All Around FET (GAAFET) Nanosheet.

Como señala la propia compañía, los transistores CFET ya se encuentran en los laboratorios de TSMC y se están sometiendo a diversas pruebas de rendimiento, eficiencia y densidad. En comparación con GAAFET, CFET ofrecerá un mejor diseño en todas esas áreas, pero requerirá ciertos pasos de fabricación adicionales para que el chip funcione según lo previsto. El CFET, que integra FET de tipo p y de tipo n en un único dispositivo, requerirá el uso de escáneres EUV de alta precisión y potencia para su fabricación.

El uso de CFET, como muestra la hoja de ruta, supone uno de los últimos pasos en el mundo del silicio. Requerirá la integración de nuevos materiales en el proceso de fabricación, lo que se traducirá en una mayor inversión en investigación y desarrollo encargada de la creación de nodos.

Kevin Zhang, vicepresidente senior de TSMC, responsable de la hoja de ruta tecnológica y el desarrollo empresarial, señala: «Permítanme hacer una aclaración sobre esa hoja de ruta, todo lo que vaya más allá de la Nanosheet es algo que pondremos en nuestra [hoja de ruta] para comunicarles que todavía queda futuro ahí fuera. Seguiremos trabajando en diferentes alternativas. También tengo que añadir que los materiales unidimensionales [basados en transistores] […], todos ellos están siendo investigados en los futuros candidatos potenciales en este momento, no le vamos a decir exactamente la arquitectura del transistor será más allá de la Nanosheet.»

Aunque la compañía está trabajando en los CFET, es posible que surja una nueva tecnología a medida que avance la investigación. Lo único «inamovible» es la tecnología GAAGET de nanosheet, que comenzará en el nodo de 2 nm. Además, Zhang añadió: «Así pues, esta Nanosheet empieza en 2nm, resulta razonable proyectar y esa Nanosheet se utilizará durante al menos un par de generaciones, ¿verdad? Si pensamos en los CFET, hemos sacado provecho de los [FinFET] durante cinco generaciones, es decir, más de 10 años. Tal vez [la estructura de los dispositivos] sea un problema que deba preocupar a otro, entonces se podrá seguir escribiendo una historia.»

Vía: TechPowerUp