Rivian presenta Autonomy+ con chip RAP1 para impulsar su plataforma autónoma

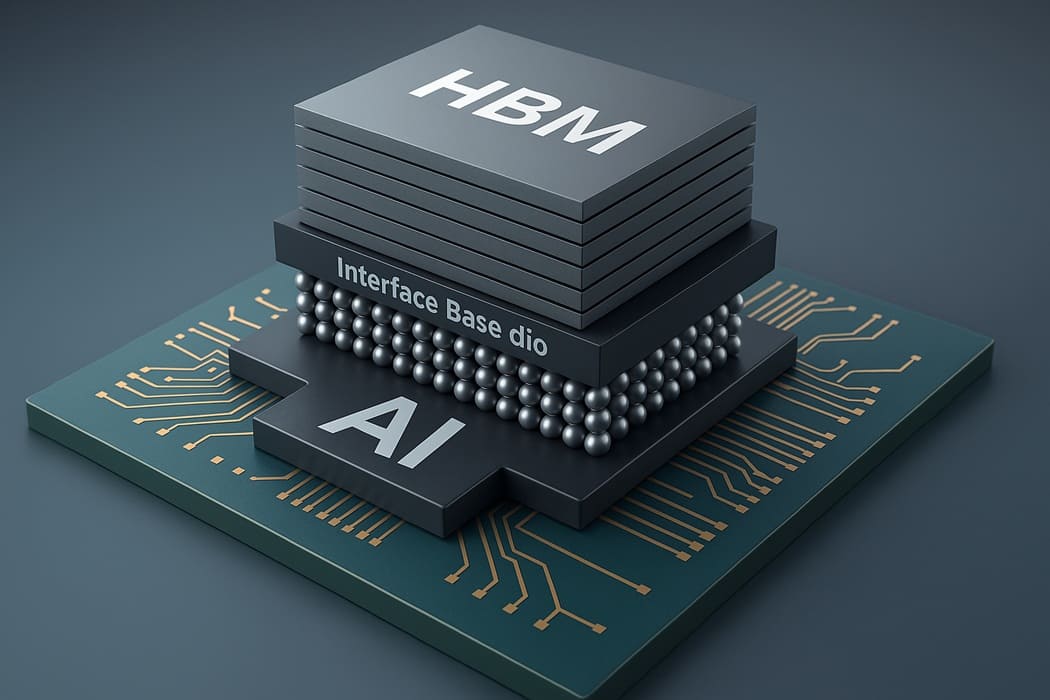

Rivian ha presentado Autonomy+, una plataforma de asistencia que combina el procesador RAP1, diseñado en el nodo 5 nm de TSMC, con 11 cámaras, múltiples módulos radar y un sensor LiDAR integrados en un conjunto orientado a maximizar la percepción del vehículo. El servicio costará 2.500$ o 50$/mes, situándose como una alternativa competitiva a soluciones … Rivian presenta Autonomy+ con chip RAP1 para impulsar su plataforma autónoma