Según el Korea Economic Daily, en 2024 Samsung tiene previsto lanzar sus servicios de encapsulado 3D para memorias HBM (High-Bandwidth Memory). Dicha información se puso de manifiesto en el Samsung Foundry Forum 2024 celebrado en San José y fue corroborada por fuentes de la industria.

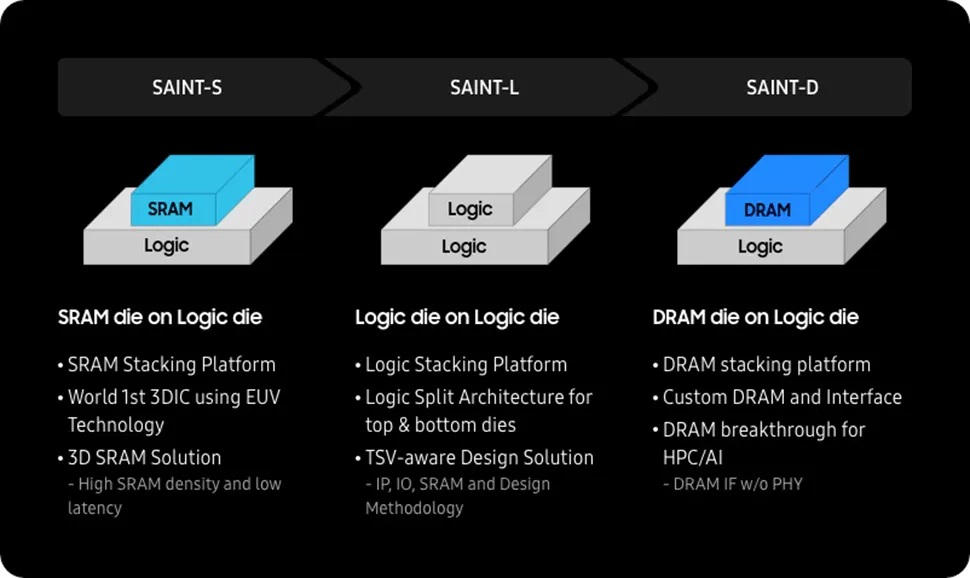

La nueva tecnología de encapsulado 3D, denominada SAINT (Samsung Advanced Interconnect Technology), abarca tres métodos de apilamiento distintos: SAINT-S para SRAM, SAINT-L para lógica y SAINT-D para apilar DRAM sobre chips lógicos como CPUs o GPUs.

Hace ya años que Samsung viene desarrollando la tecnología SAINT-D, que en 2022 anunció de forma oficial. Ahora, se prevé que la tecnología esté lista para su producción en 2024, lo que supondrá un significativo logro para la compañía, que es el principal fabricante de memorias del mundo y uno de los líderes en fundición.

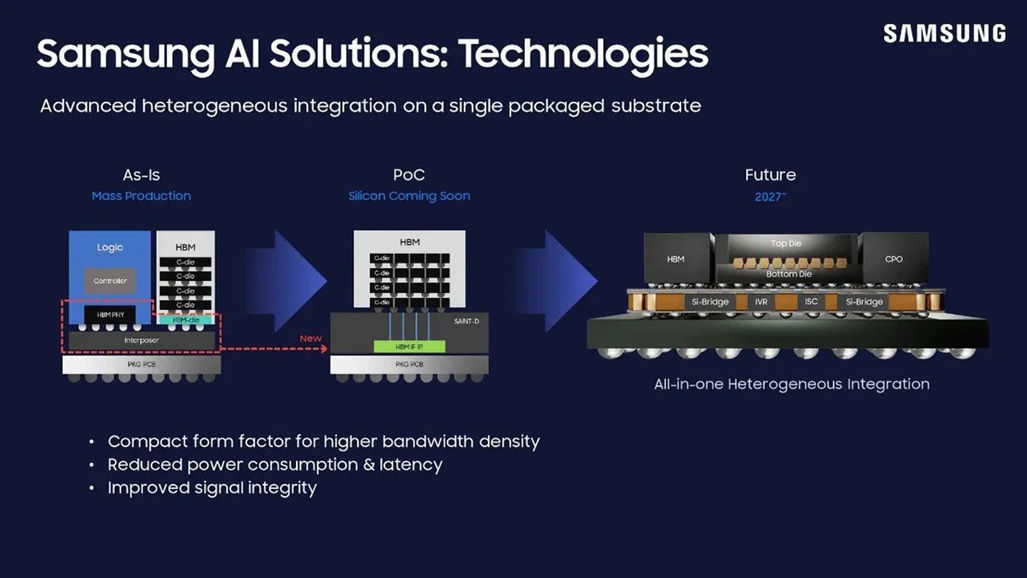

La tecnología SAINT-D permite el apilamiento vertical de chips HBM directamente sobre los procesadores, lo que constituye un punto de inflexión con respecto a la actual tecnología 2,5D que conecta los chips HBM y las GPUs de forma horizontal a través de un intercalador de silicio.

Gracias a este apilamiento vertical, se elimina la necesidad del intercalador de silicio, si bien es necesario un nuevo die base para la memoria HBM, que se fabrica utilizando una avanzada tecnología de proceso. Entre las ventajas de este encapsulado 3D están la mayor velocidad de transferencia de datos, la limpieza de las señales, la reducción del consumo energético y la disminución de las latencias. Ahora bien, estas ventajas conllevan unos costes de encapsulado relativamente elevados.

Samsung tiene previsto ofrecer este avanzado encapsulado 3D de HBM como un servicio llave en mano. Es decir, su división de memoria producirá chips HBM y la unidad de fundición ensamblará los procesadores para empresas sin fábrica.

No están claros los detalles exactos de lo que Samsung pretende ofrecer con SAINT-D este año. La integración de HBM en un die lógico requiere un diseño de chip apropiado, y se desconoce la existencia de procesadores de grandes compañías diseñados para albergar HBM en su parte superior y cuyo lanzamiento esté previsto para 2024 o la primera mitad de 2025.

Con vistas al futuro, el propósito de Samsung es introducir la tecnología de integración heterogénea «todo en uno» en 2027. Dicha tecnología posibilitará la integración de dos capas de chips lógicos, memoria HBM en un intercalador e incluso ópticas de coencapsulado (CPO).

Vía: Guru3D