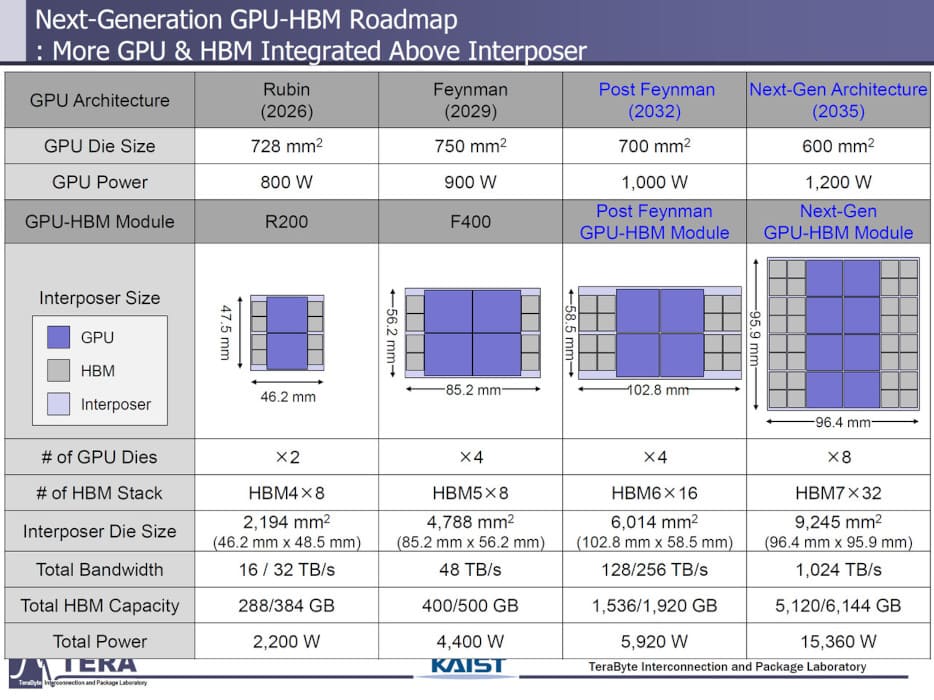

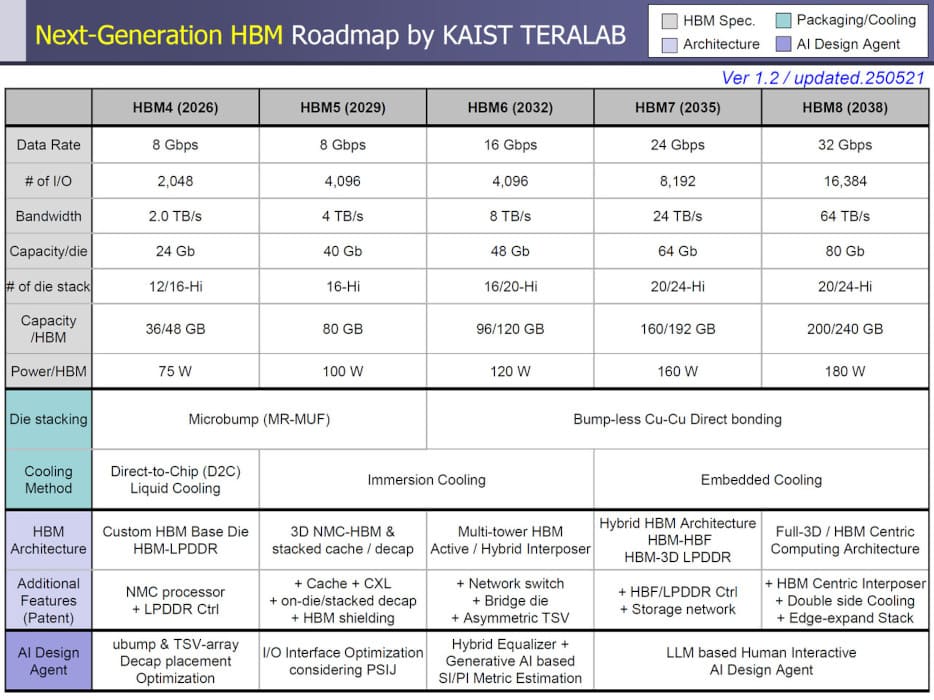

El futuro de la memoria HBM ha quedado más definido tras una presentación conjunta del KAIST Memory Systems Laboratory y el grupo TERA Interconnection and Packaging, donde desvelaron la evolución prevista de los estándares HBM4 hasta HBM8. Este ambicioso roadmap, compartido por Wccftech y VideoCardz, anticipa mejoras drásticas en ancho de banda, densidad, eficiencia energética y tecnologías de empaquetado, orientadas a plataformas de aceleración para centros de datos e inteligencia artificial.

HBM4 en 2026: 2 TB/s por stack y hasta 432 GB por tarjeta

El primer paso será HBM4, previsto para 2026. Cada pila alcanzará 2 TB/s de ancho de banda con un pin rate de 8 Gbps y una interfaz de 2.048 bits. Las pilas apiladas crecerán a entre 12 y 16 capas, con capacidades por paquete de 36 a 48 GB y un consumo de 75W.

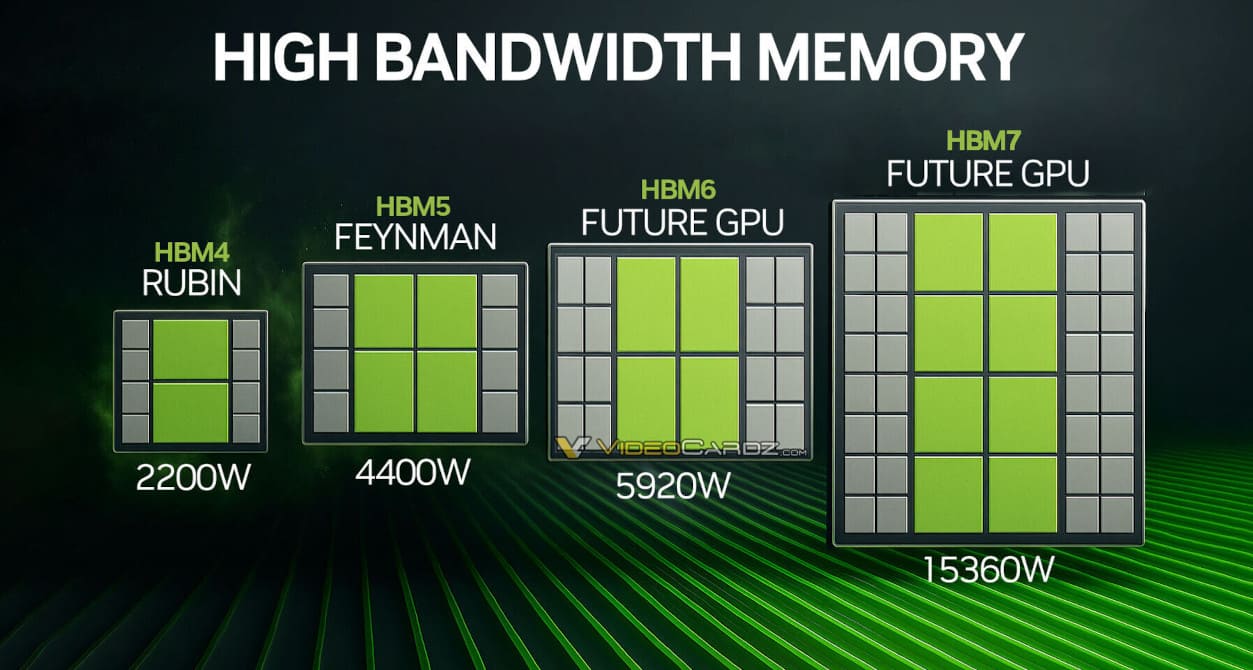

Entre los primeros productos que adoptarán esta tecnología están las NVIDIA Rubin Ultra, que duplicarán el número de pilas de memoria de ocho a dieciséis, y las AMD Instinct MI500, que aspiran a integrar hasta 432 GB por dispositivo.

HBM5 a HBM6: escalando hasta 8 TB/s y 120 GB por stack

En 2029, llegará HBM5 con el mismo pin rate pero doblando las líneas I/O a 4.096 bits, lo que permitirá 4 TB/s por stack y hasta 80 GB por paquete. Se espera que el primer chip en usarlo sea el NVIDIA Feynman, con una potencia total superior a 4.400W y capacidades entre 400 y 500 GB.

En 2032, HBM6 duplicará la velocidad a 16 Gbps, alcanzando 8 TB/s por stack con 20 capas de 40 Gb cada una. El consumo subirá a 120W, e incluirá tecnologías como bonding sin bumps de cobre y refrigeración por inmersión como estándar.

HBM7 y HBM8: hasta 64 TB/s, 240 GB por stack y diseños chiplet

Para 2035, HBM7 ofrecerá 24 Gbps, 8.192 bits de interfaz, 24 TB/s por stack y hasta 192 GB con 160W. NVIDIA estaría preparando un acelerador de 15.360W para esta generación.

Por último, HBM8 previsto para 2038, promete 32 Gbps, interfaces de 16.384 bits, 64 TB/s por stack, y entre 200 y 240 GB por pila, con refrigeración embebida y consumo de hasta 180W.

Además, se barajan arquitecturas híbridas HBM-HBF, que combinarían DRAM con memoria flash de alto ancho de banda (High-Bandwidth Flash) mediante vias TSV ultrarrápidas, con vistas a entornos de inferencia IA a escala petabyte.

Vía: TechPowerUp