El sector de los semiconductores avanzados podría sumar un nuevo frente competitivo en los próximos años. La fundición japonesa Rapidus ha desarrollado un prototipo de encapsulado a nivel de panel (PLP) basado en un interposador de vidrio, una tecnología pensada para aceleradores de IA de alto rendimiento que buscan ir más allá de las limitaciones tradicionales de las obleas de silicio de 300 mm.

El prototipo será mostrado esta semana en SEMICON Japan 2025, celebrada en Tokio, y marca un paso relevante en la estrategia de Rapidus para ofrecer alternativas avanzadas de fabricación y encapsulado frente al dominio de TSMC. La propuesta sustituye las obleas circulares convencionales por grandes paneles cuadrados de vidrio, diseñados para integrar GPUs multi-chip junto a más de una docena de memorias HBM dentro de un mismo encapsulado.

Paneles de vidrio de gran formato para IA de nueva generación

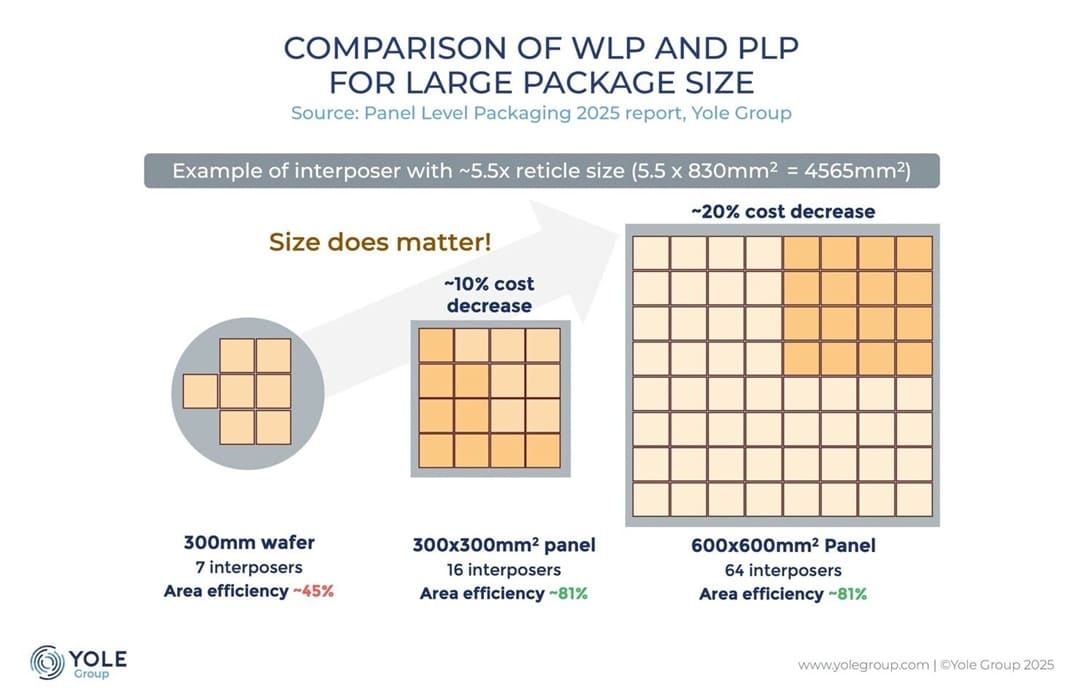

Rapidus está trabajando con paneles de vidrio de 600 × 600 mm, una superficie muy superior a la de una oblea estándar de 300 mm, lo que permite obtener un mayor número de interposadores por unidad y reducir el desperdicio de material. Este enfoque resulta especialmente atractivo para los chips de IA de próxima generación, que requieren interconexiones densas, grandes áreas activas y arquitecturas cada vez más complejas.

El uso de sustratos de vidrio ofrece ventajas claras frente a materiales orgánicos tradicionales, como una mejor planitud, mayor estabilidad dimensional y propiedades eléctricas más favorables para enlaces de alta velocidad. Estas características son clave cuando se trabaja con HBM, buses internos de gran ancho de banda y diseños multi-chip de gran tamaño.

Retos técnicos y precedentes en la industria

Pese a sus ventajas, el vidrio introduce nuevos desafíos de fabricación. Su fragilidad y la posibilidad de deformaciones (warpage) aumentan a medida que crece el tamaño del panel, lo que complica los procesos de manipulación, alineado y ensamblaje. No es una barrera menor, y explica por qué esta tecnología aún se encuentra en fase temprana.

Un precedente relevante es Intel, que recientemente decidió abandonar el desarrollo interno de sustratos de vidrio para encapsulado. En su lugar, optó por licenciar la tecnología, buscando monetizar la investigación sin comprometerse a una producción a gran escala antes de 2030. Este movimiento refleja tanto el potencial como la complejidad real de este tipo de soluciones.

Un pulso directo con las tecnologías de TSMC

Para Rapidus, el PLP con vidrio representa una oportunidad estratégica para atraer clientes que hoy dependen casi en exclusiva de TSMC y sus tecnologías de encapsulado avanzado, como Chip-on-Panel-on-Substrate (CoPoS). TSMC planea iniciar líneas piloto de CoPoS en 2026, con producción en masa prevista entre finales de 2028 y la primera mitad de 2029.

El calendario de Rapidus es muy similar. La compañía japonesa apunta a producción en volumen a 2 nm en 2027, con una capacidad estimada de 25.000 obleas al mes en su planta IIM-1. La incorporación del PLP basado en vidrio un año después situaría a Rapidus en una posición competitiva directa, tanto en nodo avanzado como en encapsulado de alto nivel.

Un escenario competitivo que empieza a tomar forma

Si los plazos se cumplen, 2028 y 2029 podrían marcar el inicio de una competencia real en el terreno del encapsulado para IA de gran escala, un área crítica para GPUs, aceleradores y mini centros de datos de próxima generación. Rapidus no solo busca fabricar silicio avanzado, sino ofrecer un ecosistema completo que combine nodos punteros y tecnologías de encapsulado diferenciadoras.

Aún quedan retos técnicos importantes por resolver, pero el movimiento confirma que la carrera por el liderazgo en IA ya no se libra solo en litografía, sino también en cómo se integran y conectan los chips. Y en ese terreno, Rapidus quiere sentarse en la misma mesa que TSMC.

Vía: TechPowerUp