Pat Gelsinger, CEO de Intel, confirmó en la sesión de preguntas y respuestas del primer día de Innovation 2023 que la compañía está desarrollando una tecnología de caché apilada en 3D para sus procesadores.

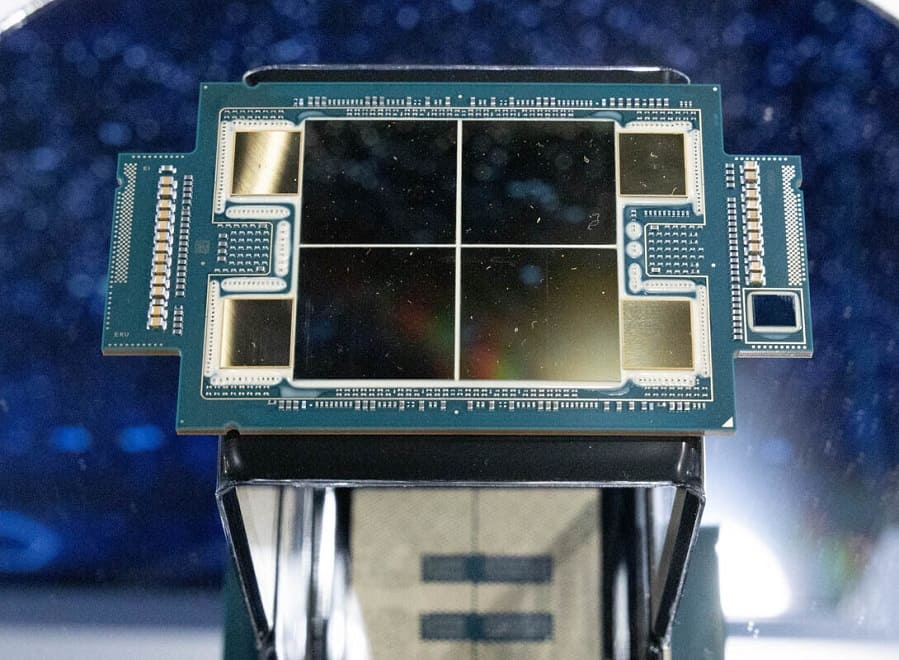

La tecnología consiste en ampliar la caché de último nivel (caché L3) de un procesador con una SRAM adicional apilada físicamente en la parte superior y unida al tejido de datos de gran ancho de banda de la caché. La caché apilada funciona a la misma velocidad que la caché en el chip, por lo que el tamaño de la caché combinada es visible para el software como un único bloque direccionable contiguo de memoria caché.

AMD ha utilizado la caché apilada 3D con buenos resultados en sus procesadores. En procesadores de cliente como la serie Ryzen X3D, la caché proporciona importantes mejoras de rendimiento en juegos, ya que la mayor caché L3 hace que los núcleos del CPU tengan acceso inmediato a más datos de renderizado del juego; mientras que en procesadores de servidor como EPYC «Milan-X» y «Genoa-X», la caché añadida proporciona importantes mejoras en cargas de trabajo de cálculo con uso intensivo de memoria.

El enfoque de Intel respecto a la caché apilada 3D será diferente a nivel de hardware en comparación con el de AMD, afirmó Gelsinger en su respuesta. La tecnología de AMD se ha desarrollado en colaboración con TSMC y se basa en una tecnología de encapsulado SoIC fabricada por TSMC que facilita la conexión de alta densidad entre el CCD y el chiplet de caché. Intel utiliza sus propias fábricas para los dies del procesador y tendrá que utilizar su propia IP.

«Cuando se hace referencia a V-Cache, se está hablando de una tecnología muy específica que TSMC hace también con algunos de sus clientes. Obviamente, lo estamos haciendo de manera diferente en nuestra composición, ¿verdad? Y ese tipo concreto de tecnología no forma parte de Meteor Lake, pero en nuestra hoja de ruta vemos la idea del silicio 3D, en el que tendremos la caché en un die y el cálculo del CPU en el die apilado encima y, obviamente, mediante EMIB y Foveros podremos componer diferentes capacidades», explica Gelsinger.

«Estamos muy satisfechos de nuestras avanzadas capacidades para arquitecturas de memoria de nueva generación, ventajas para el apilamiento 3D, tanto para pequeños dies como para packs de gran tamaño para IA y servidores de alto rendimiento. Disponemos de una amplia gama de estas tecnologías. Las utilizaremos en nuestros productos y las presentaremos también a los clientes de Foundry (IFS)», añadió.

Recientemente, Intel ha ofrecido un análisis en profundidad de la arquitectura de su próximo procesador cliente «Meteor Lake«, en el que su tecnología de encapsulado Foveros y las interconexiones de tile a tile permiten que los distintos tiles (chiplets) funcionen como un silicio cohesionado. En concreto, Intel parece haber resuelto los problemas de latencia derivados de tener la iGPU, los núcleos del CPU y los controladores de memoria en tiles separados.

Vía: TechPowerUp