NVIDIA estaría encontrando dificultades en el desarrollo del Rubin Ultra, su próxima arquitectura de silicio de GPU para IA, debido a limitaciones en el empaquetado avanzado de TSMC. Según diversas filtraciones, el diseño podría superar las capacidades actuales al intentar integrar grandes volúmenes de memoria HBM y múltiples dies en un único encapsulado.

Este escenario contrasta con el estado del Rubin estándar, del que ya existen muestras funcionales y cuyo despliegue está previsto para este verano. El problema no estaría en el rendimiento del chip, sino en la viabilidad física del encapsulado, un aspecto que cada vez condiciona más el desarrollo de hardware en el sector de IA.

Un diseño extremadamente ambicioso: más dies y más HBM en un solo paquete

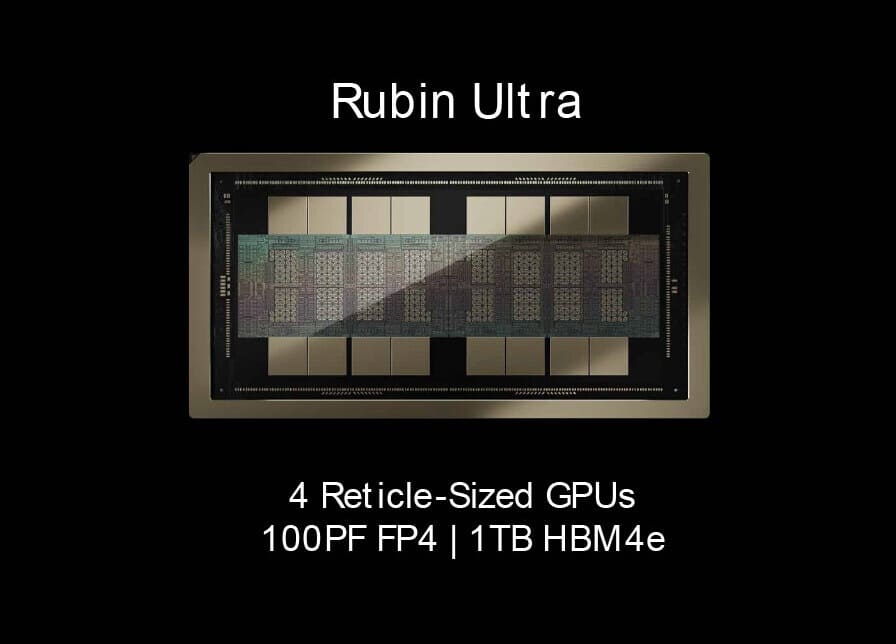

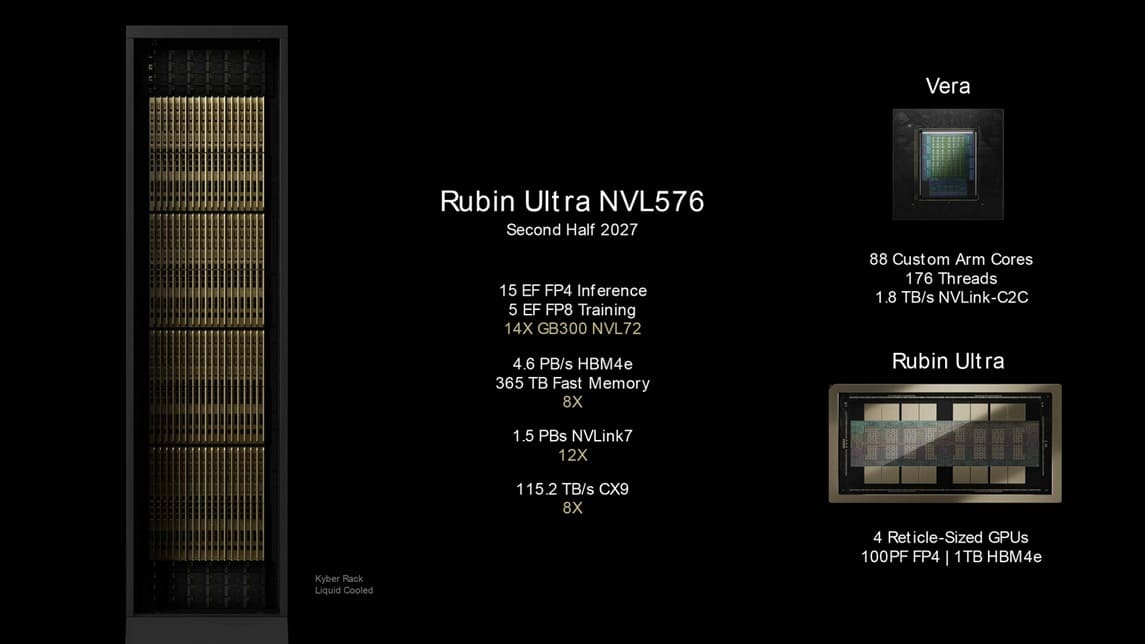

El salto de Rubin a Rubin Ultra implica duplicar la complejidad del encapsulado. El diseño pasaría de un paquete con 2 dies y 8 módulos HBM4 a una configuración con 4 dies y hasta 16 módulos HBM4E, aumentando de forma notable la densidad de integración dentro del mismo espacio físico.

Este enfoque busca impulsar el rendimiento en aceleración de IA, pero introduce retos claros en gestión térmica, distribución de señal y estabilidad estructural. La combinación de más silicio de GPU y mayor cantidad de memoria dentro de un mismo paquete incrementa el riesgo de problemas mecánicos y eléctricos.

CoWoS-L en el límite: deformación y contacto imperfecto

El empaquetado CoWoS-L de TSMC estaba diseñado para manejar configuraciones complejas, pero en escenarios tipo 2+2 dies comienzan a aparecer limitaciones claras. En este caso, el problema principal estaría en la deformación del sustrato, que se dobla en varias direcciones debido al tamaño y densidad del conjunto.

Este comportamiento provoca un contacto incompleto entre los dies y la base, lo que compromete tanto la estabilidad eléctrica como la disipación térmica. En la práctica, esto introduce una limitación real al escalado del diseño, más allá de lo que permitiría la arquitectura sobre el papel.

CoPoS como alternativa: paneles más grandes para reducir tensiones

Ante estas limitaciones, TSMC estaría explorando CoPoS (Chip-on-Panel-on-Substrate), una alternativa que sustituye los interposers tradicionales por paneles de mayor tamaño. Este enfoque permite distribuir mejor los dies y módulos HBM, reduciendo la tensión mecánica del encapsulado y mejorando la estabilidad global del conjunto.

Los primeros formatos parten de 310 × 310 mm, con previsión de escalar a 515 × 510 mm e incluso 750 × 620 mm. Este incremento facilita integrar más componentes y optimiza el uso de superficie, algo clave en diseños de aceleradores de IA cada vez más complejos.

Interesting. It seems the reason there have been so many recent CoPoS rumors is that Rubin Ultra may have had a warpage issue in packaging.

Rubin Ultra’s warpage issue could accelerate the adoption of CoPoS. pic.twitter.com/eKlHixAwdB

— Jukan (@jukan05) March 31, 2026

Calendario en conflicto: diseño adelantado a la tecnología disponible

El principal desafío no está solo en la ingeniería, sino en el calendario. Mientras que Rubin Ultra apunta a un posible lanzamiento en 2027, la tecnología CoPoS no alcanzaría una fase madura hasta 2028 o 2029, lo que genera un desfase importante entre diseño y fabricación.

Este contexto obliga a NVIDIA a replantear su hoja de ruta, ya sea ajustando la configuración del encapsulado, reduciendo la densidad de integración o dependiendo de mejoras en CoWoS-L. En cualquier caso, el límite ya no está en el chip, sino en su integración física.

El empaquetado como nuevo cuello de botella en IA

El caso de Rubin Ultra refleja un cambio estructural en el sector de semiconductores, donde el límite ya no reside únicamente en la litografía, sino en la capacidad de integrar múltiples componentes en un mismo encapsulado funcional. Este cambio afecta directamente al ritmo de evolución del hardware.

Tecnologías como CoWoS y CoPoS pasan a ser determinantes, ya que condicionan cuántos dies y módulos HBM pueden combinarse sin comprometer la estabilidad. En este escenario, el empaquetado avanzado se convierte en un factor crítico para el futuro de la IA y computación de alto rendimiento.

Vía: TechPowerUp