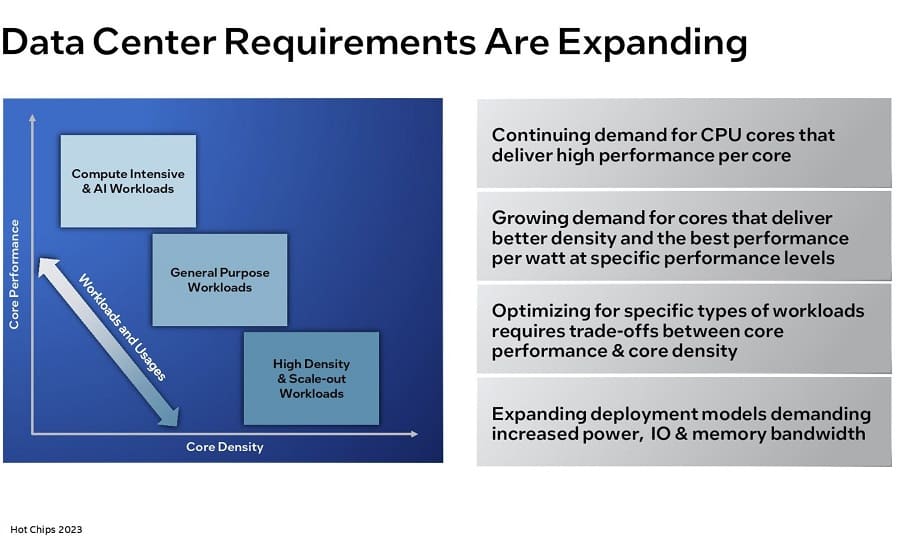

Intel presentó en el evento Innovation 2023 una variante de 288 núcleos del procesador Xeon «Sierra Forest«, destinada a servidores de alta densidad para entornos de escalabilidad horizontal y nativos de la nube.

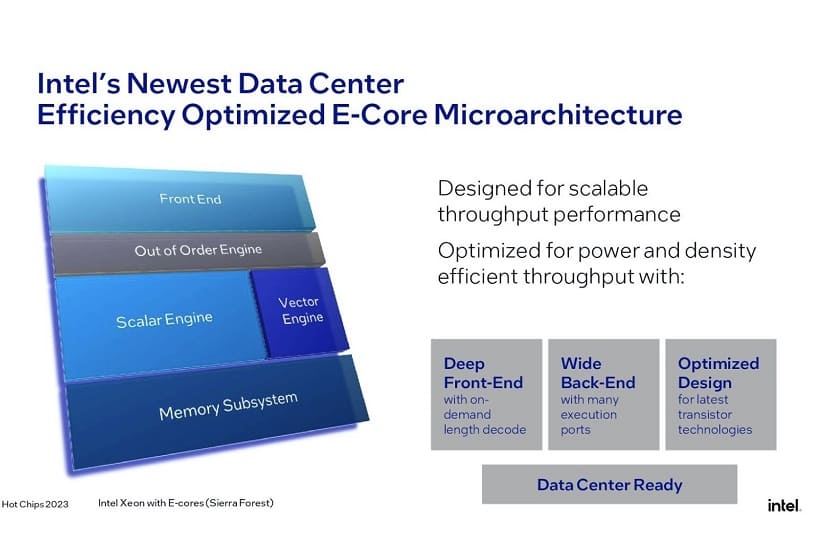

Viene a suceder al modelo actual de 144 núcleos. «Sierra Forest» se trata de un procesador para servidores basado íntegramente en núcleos de eficiencia, o E-cores, basados en la microarquitectura de núcleos «Sierra Glen», un derivado para servidores de «Crestmont», la segunda generación de E-core de Intel que debuta en clientes con «Meteor Lake».

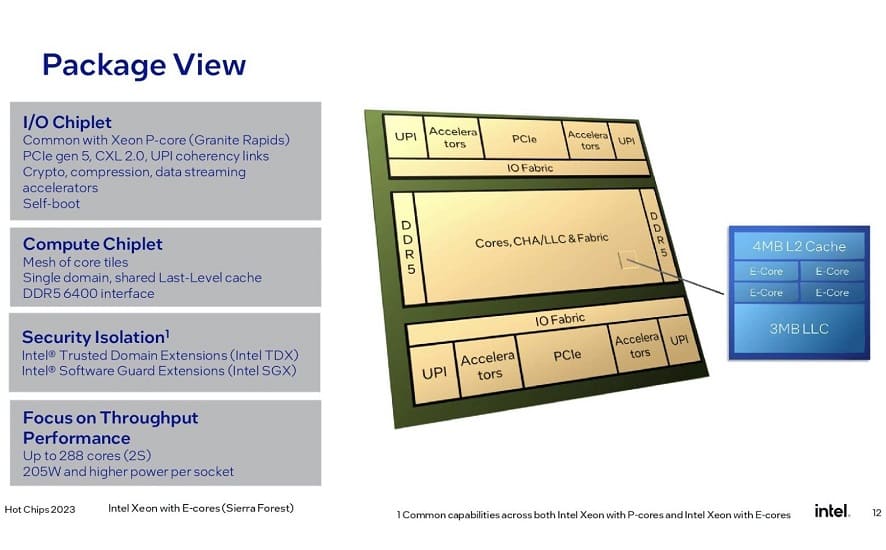

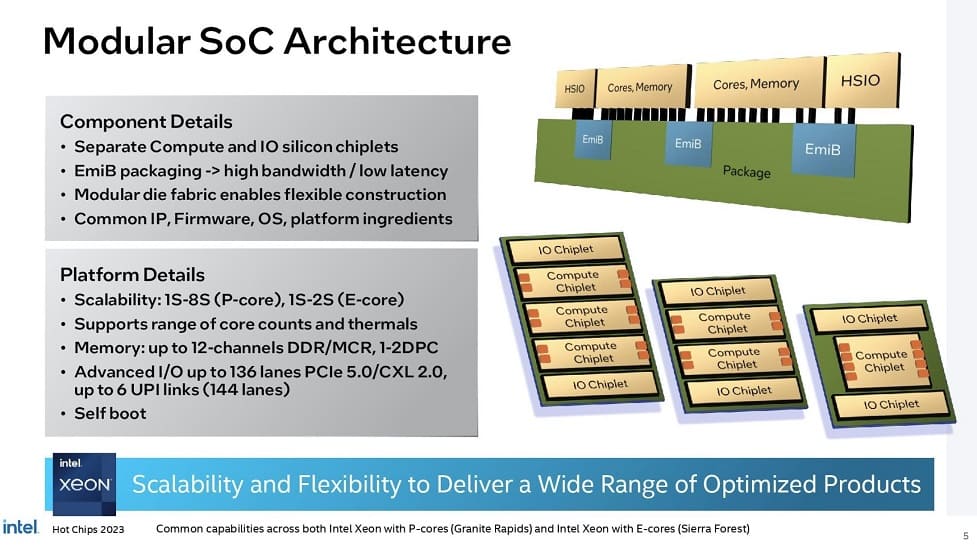

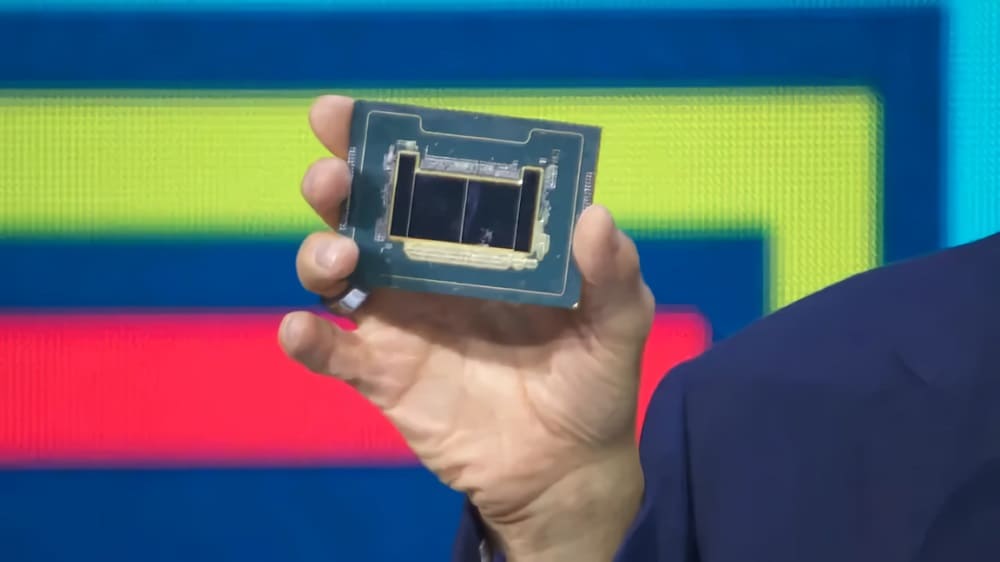

Xeon «Sierra Forest» es un procesador basado en chiplets, muy similar a «Meteor Lake» y al próximo procesador para servidores «Emerald Rapids». Cuenta con un total de cinco tiles: dos Compute tiles, dos I/O tiles y un tile base (intercalador).

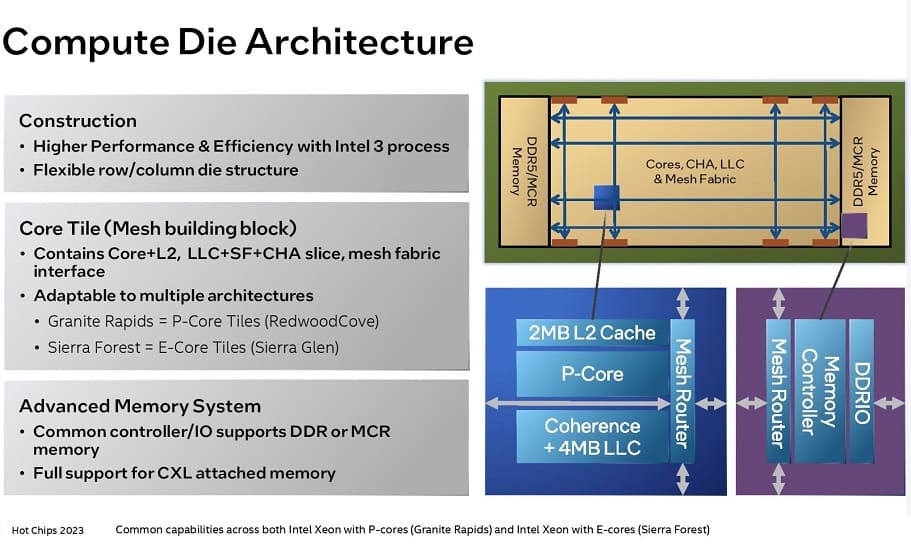

Cada uno de los dos Compute tiles está construido sobre el nodo de fundición Intel 3, un nodo más avanzado que el Intel 4, con librerías de mayor densidad y un incremento no revelado del rendimiento/vatio. Cada tile cuenta con 36 clusters E-core «Sierra Glen«, 108 MB de caché L3 compartida, controladores de memoria DDR5 de 6 canales (12 subcanales) e interfaces Foveros de tile a tile.

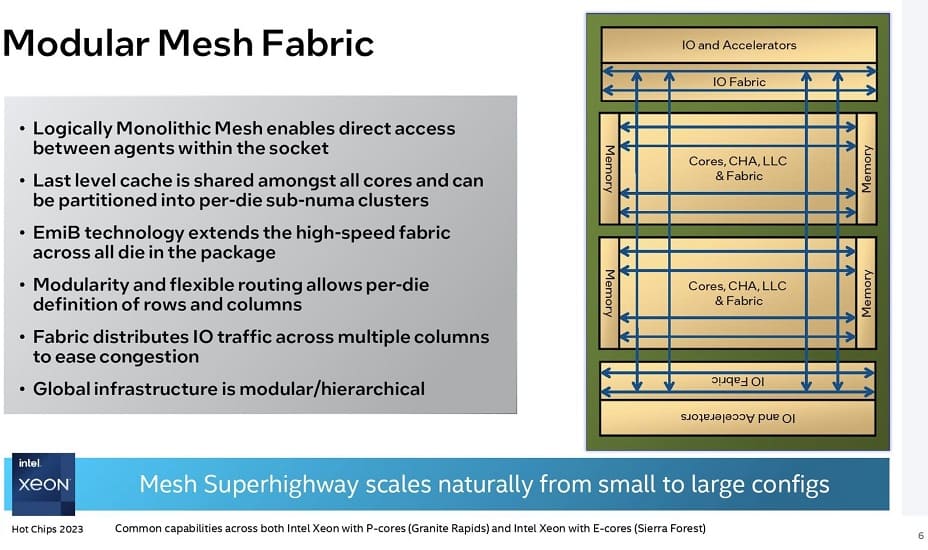

Cada clúster E-core de «Sierra Glen» cuenta con cuatro núcleos de CPU que comparten una caché L2 local de 4 MB y un segmento de 3 MB que contribuye a la caché L3 de 108 MB del tile. A diferencia del Compute tile «Meteor Lake», que emplea un bus de anillo para conectar sus clústeres de núcleos E y núcleos P, el Compute tile utiliza una topología de interconexión en malla para el gran conjunto de 36 clústeres de núcleos E.

Con 144 núcleos por tile, en su configuración máxima con tres de estos tiles, «Sierra Forest« alcanza los 288 núcleos. «Sierra Glen» carece de SMT, al igual que «Crestmont», por lo que el SO solo tiene 288 procesadores lógicos a los que dirigirse.

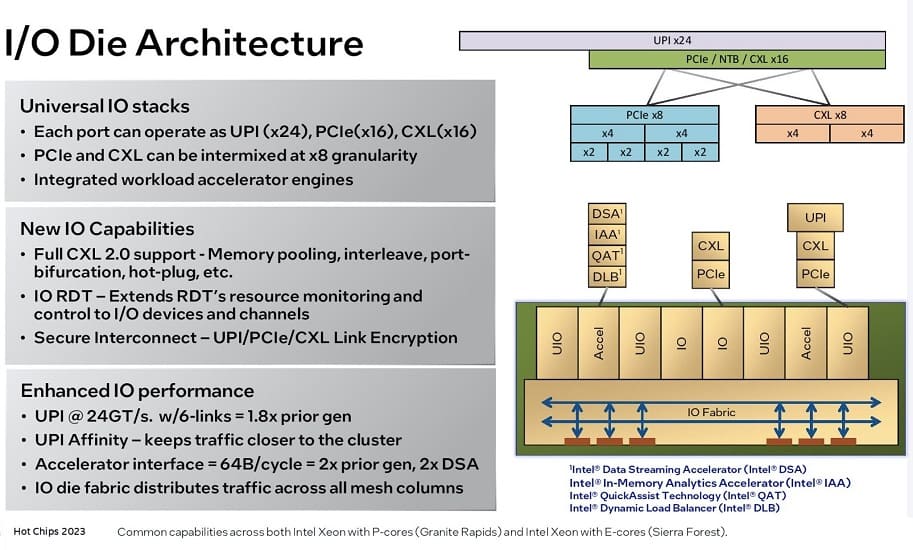

Además de los dos «Compute tiles», el procesador cuenta con dos «I/O tiles«. En contraste con el «I/O tile» de nombre similar del procesador cliente «Meteor Lake», los del «Sierra Forest» cumplen funciones tanto de SoC como de I/O PHY. Con los controladores de memoria situados en los «Compute tiles», en su variante máxima de 288 núcleos, «Sierra Forest» cuenta con una interfaz de memoria DDR5 de 12 canales.

El I/O tile se queda con la interconexión UPI para servidores 2P; aceleradores específicos de aplicaciones, un complejo raíz PCI-Express Gen 5 de 68 líneas que es flexible entre PCIe Gen 5 y CXL 2.0, y el I/O Fabric. A pesar de basarse en un nodo avanzado como Intel 3, cada uno de los dos Compute tiles ocupa una enorme superficie de 578 mm², mientras que cada uno de los dos I/O tiles ocupa 241 mm².

La interfaz de memoria de hasta 12 canales de «Sierra Forest« es compatible de forma nativa con la velocidad ECC DDR5-6400. Los aceleradores proceden del actual procesador «Granite Rapids» y proporcionan mejoras de velocidad para las operaciones más habituales de criptografía, transmisión de archivos y compresión de datos.

Cuando llegue en la primera mitad de 2024, Xeon «Sierra Forest» se enfrentará al procesador EPYC «Bergamo» de AMD. «Bergamo» se basa en una filosofía ligeramente diferente a la de «Sierra Forest». Se trata de un procesador de 128 núcleos y 256 hilos basado en núcleos «Zen 4c» que no llegan a calificarse como núcleos E y tienen un IPC idéntico al de los núcleos «Zen 4» estándar, así como una ISA y un SMT idénticos.

Vía: TechPowerUp