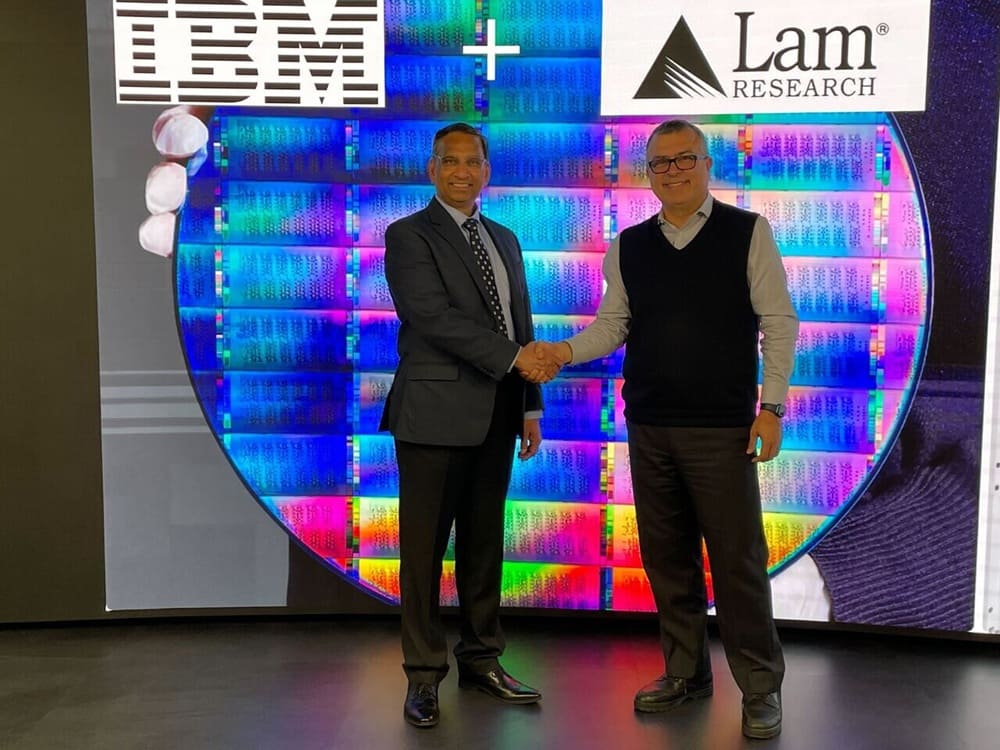

El avance hacia nodos de fabricación por debajo de 1 nm representa uno de los mayores retos actuales dentro del sector de semiconductores. Tras el desarrollo de tecnologías de 2 nm y 3 nm, la industria se enfrenta a una etapa en la que el escalado tradicional empieza a encontrar límites físicos cada vez más complejos. En este contexto, IBM y Lam Research han anunciado una colaboración centrada en el desarrollo de nuevos materiales, procesos de fabricación avanzados y técnicas de litografía High-NA EUV orientadas a continuar reduciendo el tamaño de los transistores en futuras generaciones de chips.

Ambas compañías mantienen una relación tecnológica desde hace más de una década dentro del ámbito de la fabricación lógica avanzada, participando en el desarrollo de tecnologías clave como los transistores nanosheet o la introducción de litografía EUV en procesos modernos. El nuevo acuerdo, con un horizonte de cinco años, amplía esa cooperación para investigar tecnologías que permitan extender el escalado de los chips más allá de los nodos actuales.

Nuevos materiales y procesos para arquitecturas de próxima generación

A medida que los nodos de fabricación se acercan a escalas subnanométricas, la complejidad de los dispositivos aumenta de forma considerable. La industria está explorando nuevas arquitecturas de transistor como nanosheet y nanostack, así como métodos avanzados de interconexión que permitan mantener el rendimiento eléctrico y la eficiencia energética a pesar de la reducción de tamaño.

La colaboración entre IBM y Lam Research se centrará en el desarrollo de nuevos materiales y procesos de deposición y grabado (etch) capaces de fabricar estas estructuras con mayor precisión. Estos procesos son fundamentales para construir transistores más densos y complejos sin comprometer su estabilidad ni su comportamiento eléctrico.

Otro de los elementos que está cobrando importancia en nodos avanzados es el uso de backside power delivery, una técnica que desplaza parte del sistema de alimentación eléctrica a la cara posterior del chip para mejorar la distribución de energía y reducir interferencias en las capas superiores del dispositivo.

High-NA EUV como siguiente paso en la litografía avanzada

Uno de los pilares de esta colaboración será el desarrollo de procesos compatibles con litografía High-NA EUV, la evolución de la litografía ultravioleta extrema utilizada actualmente en nodos avanzados.

Esta tecnología aumenta la apertura numérica del sistema óptico utilizado en las máquinas EUV, permitiendo proyectar patrones más pequeños y con mayor precisión sobre las obleas de silicio. Sin embargo, el salto a High-NA EUV implica rediseñar parte del proceso de fabricación, incluyendo nuevos materiales fotoresist, técnicas de grabado y procesos de deposición adaptados a las nuevas dimensiones.

Lam Research aportará varias de sus plataformas industriales utilizadas en procesos de fabricación avanzada, incluyendo tecnologías de dry resist, sistemas de etch de alta precisión y herramientas de deposición que permitirán desarrollar flujos completos de fabricación para nodos sub-1 nm.

Investigación conjunta en el Albany NanoTech Complex

Gran parte del trabajo se llevará a cabo en el NY Creates Albany NanoTech Complex, un centro de investigación dedicado al desarrollo de tecnologías de fabricación de semiconductores avanzadas.

Estas instalaciones permiten experimentar con nuevos materiales, arquitecturas de transistor y técnicas de litografía antes de su posible adopción en líneas de producción industriales. Dentro de este proyecto, el objetivo será validar flujos de fabricación completos para dispositivos nanosheet y nanostack, así como evaluar su viabilidad en combinación con High-NA EUV y nuevos esquemas de alimentación eléctrica como backside power delivery.

En la actualidad, el desarrollo de nodos sub-1 nm depende cada vez más de una combinación de avances en arquitectura de dispositivos, materiales, litografía y empaquetado avanzado, lo que explica la importancia de colaboraciones tecnológicas entre empresas especializadas en distintos segmentos de la cadena de fabricación de chips.

Vía: TechPowerUp