La firma ha dado un paso clave en el desarrollo de interconexiones chiplet de alta velocidad. Cadence ha completado el cierre de diseño (tape-out) de su IP UCIe de tercera generación, alcanzando 64 Gbps por carril sobre el proceso N3P de 3 nm de TSMC, con un claro enfoque en arquitecturas de IA, HPC y sistemas avanzados de centro de datos.

El avance llega en un momento en el que el sector de semiconductores se enfrenta a diseños cada vez más complejos, donde la conectividad entre chiplets resulta tan crítica como el propio silicio de CPU o GPU. A medida que los nodos bajan de 3 nm, el equilibrio entre consumo, rendimiento y área se convierte en uno de los principales retos para los diseñadores de SoC de última generación.

UCIe Gen3 y el salto a 64 Gbps por carril

El nuevo subsistema IP de UCIe Gen3 eleva de forma notable el listón frente a generaciones anteriores. Con 64 Gbps por carril, permite alcanzar densidades de ancho de banda muy elevadas, facilitando arquitecturas chiplet escalables sin recurrir a buses internos cada vez más complejos o ineficientes. Este enfoque resulta clave para aceleradores de IA, procesadores HPC y soluciones de red de alto rendimiento.

Desde el punto de vista de integración, la IP mantiene compatibilidad completa con la especificación UCIe, lo que garantiza interoperabilidad dentro de ecosistemas multi-vendedor. Esto es especialmente relevante en un contexto donde los diseños heterogéneos combinan chiplets de diferentes orígenes, encapsulados bajo un mismo sistema.

Eficiencia energética y proceso N3P de 3 nm

Uno de los aspectos más relevantes del tape-out es el uso del proceso N3P de TSMC, orientado a mejorar el compromiso entre rendimiento y eficiencia energética. Gracias a este nodo, la solución UCIe Gen3 logra altas velocidades de transferencia manteniendo presupuestos energéticos ajustados, un requisito cada vez más crítico en centros de datos y sistemas de inferencia de IA.

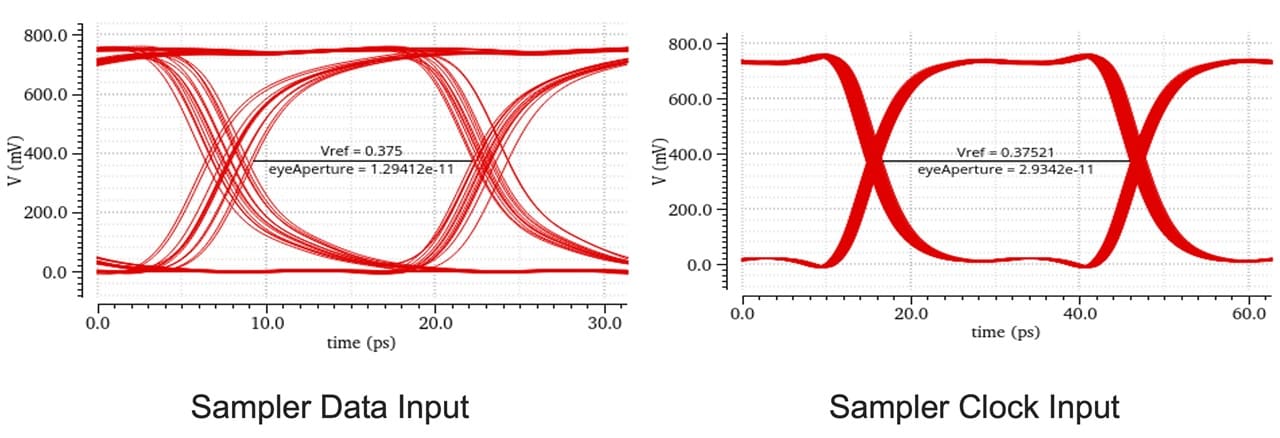

En nodos tan avanzados, la comunicación die-to-die introduce desafíos adicionales en integridad de señal, variaciones de voltaje y control térmico. La arquitectura presentada aborda estos puntos mediante técnicas avanzadas de diseño del PHY, pensadas para operar de forma estable en entornos multi-die complejos y de alta densidad.

Flexibilidad de protocolos e integración en sistemas avanzados

La IP de Cadence destaca también por su amplio soporte de protocolos, lo que facilita su adopción en múltiples escenarios de uso. Entre los interfaces compatibles se incluyen:

- AXI

- CXS.B

- CHI-C2C

- PCIe

- CXL / CXL.io

Esta versatilidad permite integrar la interconexión UCIe en aceleradores de IA, sistemas HPC, equipamiento de red y plataformas de centro de datos, reduciendo tiempos de diseño y validación. Además, la arquitectura incorpora mecanismos avanzados de corrección de errores, lane margining y capacidades de diagnóstico, orientados a garantizar fiabilidad en configuraciones heterogéneas.

Implicaciones para el sector de semiconductores

La disponibilidad de una IP UCIe a 64 Gbps sobre 3 nm refuerza la transición del sector hacia diseños chiplet modulares, más escalables y eficientes que los monolíticos tradicionales. Para fabricantes y diseñadores, este tipo de soluciones abre la puerta a sistemas multi-die más complejos, manteniendo controlados tanto el consumo como la latencia.

Con este tape-out, Cadence amplía su cartera de IP avanzada y consolida su posición en un segmento clave para el futuro del sector de IA, HPC y semiconductores de alto rendimiento, donde la interconexión entre chiplets se ha convertido en un factor determinante.

Vía: TechPowerUp