Por lo que parece, existe el procesador AMD Strix Halo, y es enorme. Dicho chip pretende plantar cara a los M3 Pro y M3 Max de Apple, permitiendo a los portátiles ultraligeros disponer de un excelente rendimiento gráfico.

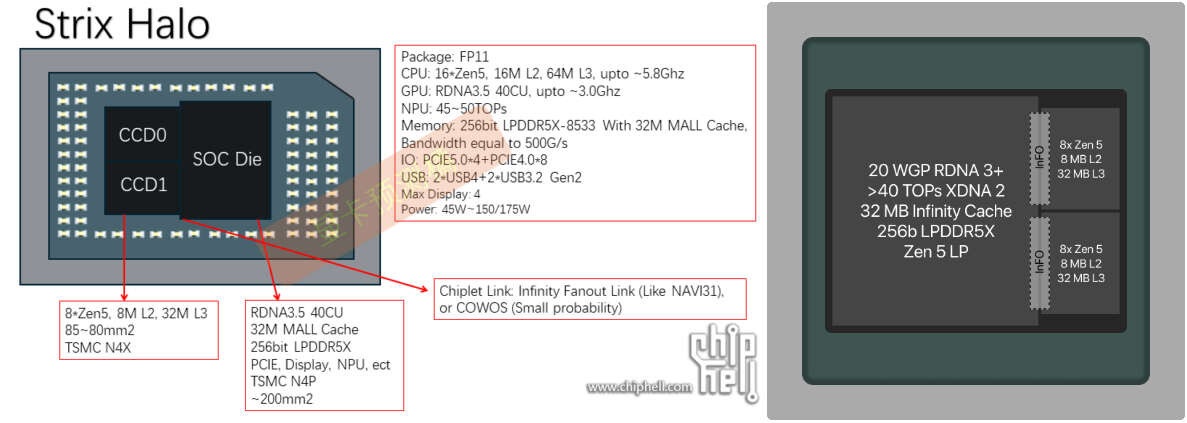

Strix Halo consiste en un procesador basado en chiplets, similar al Raphael de sobremesa con socket y al Dragon Range para portátiles con BGA, formado por uno o dos CCDs que contienen núcleos de CPU conectados a un gran chip, que técnicamente constituye el cIOD (client I/O die), pero que alberga una iGPU sobredimensionada así como una NPU. Strix Halo pretende eliminar la necesidad de una GPU dedicada al segmento de rendimiento, ahorrando espacio en el PCB.

Según las filtraciones recogidas por Harukaze5719, un conocido experto en filtraciones sobre productos AMD, el procesador Strix Halo se presenta en un encapsulado BGA denominado FP11, que tiene un tamaño de 37,5 mm x 45 mm, considerablemente mayor que el tamaño de 25 mm x 40 mm del encapsulado BGA FP8 en el que se basan los procesadores portátiles Strix Point, Hawk Point y Phoenix.

Su superficie es mayor que la del encapsulado FL1 BGA de 40 mm x 40 mm de los procesadores para portátiles gaming Dragon Range y los futuros Fire Range. Además, Strix Halo incorpora uno o dos de los mismos CCDs Zen 5 de 4 nm presentes en los procesadores Granite Ridge de sobremesa y Fire Range para portátiles, si bien, como ya hemos mencionado, están conectados a un I/O Die mucho mayor.

Se desconoce, al menos por el momento, el nodo de fundición del I/O Die del Strix Halo, si bien resulta improbable que se trate del mismo nodo de 6 nm que el cIOD que AMD ha venido haciendo uso en sus otros procesadores cliente basados en Zen 4 y Zen 5. Por tanto, no sería de extrañar que AMD esté recurriendo al mismo nodo de 4 nm que ya utilizó en Phoenix para este I/O Die.

Esta iGPU de gran tamaño cuenta con la friolera de 20 WGPs (Workgroup Processors) o 40 CUs (Compute Units), lo que equivale a 2.560 Stream Processors, 80 AI Accelerators y 40 Ray Accelerators. Dicha iGPU se basa en la más reciente arquitectura gráfica RDNA 3.5.

La iGPU, por ejemplo, del procesador convencional Strix Point de 4 nm, dispone de 8 WGPs (16 CUs, 1.024 Stream Processors). Además, tenemos la NPU. Se espera que AMD incorpore la misma NPU XDNA 2 con capacidad para 50 TOPS que incorpora el Strix Point convencional en el I/O Die del Strix Halo, dotando al procesador de funciones Microsoft Copilot+.

Durante bastante tiempo, ha sido toda una incógnita la interfaz de memoria del Strix Halo. Por lógica, resulta una pésima idea que 16 núcleos de CPU Zen 5 y una GPU de 40 Compute Units compartan incluso una interfaz de memoria DDR5 dual-channel estándar a las velocidades más elevadas disponibles, ya que tanto el CPU como la iGPU experimentarían una grave escasez de ancho de banda. Además, también hay que tener en cuenta la NPU, ya que la inferencia de IA es una aplicación susceptible a la memoria.

Existe una hipótesis según la cual, además de una interfaz LPDDR5X para los núcleos del CPU, el encapsulado de Strix Halo dispone de cableado para memoria GDDR6 dedicada. Ni siquiera una interfaz de memoria GDDR6 relativamente limitada de 128 bits a 20 Gbps otorgaría a la iGPU un ancho de banda de memoria de 320 GB/s, lo que resulta más que suficiente para los gráficos del segmento de rendimiento.

Esto significaría que, además de los chips LPDDR5X, habría cuatro chips GDDR6 en el PCB. Además, la iGPU dispone de 32 MB de memoria Infinity Cache en el propio die, lo cual parece estar en línea con la hipótesis según la cual la interfaz GDDR6 de 128 bits está exclusivamente reservada a la iGPU.

Vía: TechPowerUp