Los primeros resultados de ingeniería de los futuros AMD EPYC Venice basados en Zen 6 han aparecido en bases de datos de pruebas, ofreciendo un adelanto del rendimiento y de la nueva plataforma Socket SP7. Estas filtraciones muestran configuraciones con un alto número de núcleos orientadas a centros de datos, lo que confirma el salto generacional frente a la familia EPYC Turin actualmente en el mercado.

En este caso, se han detectado varias placas de validación interna identificadas como Congo, Kenya y Nigeria, utilizadas para probar diferentes variantes del silicio. Estas plataformas permiten evaluar el comportamiento del procesador en escenarios reales, y en conjunto reflejan una evolución clara en densidad, rendimiento y escalabilidad dentro del sector de CPU para centros de datos, donde cada mejora impacta directamente en eficiencia y capacidad de cómputo.

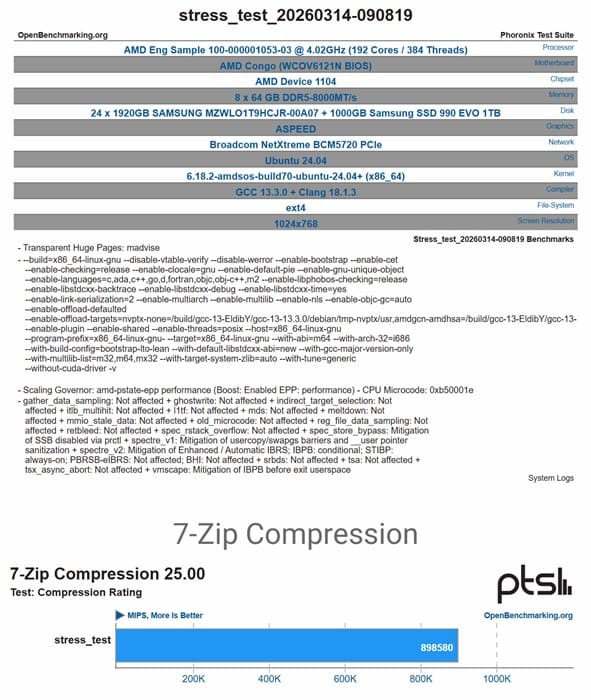

Configuraciones de hasta 192 núcleos y 384 hilos en muestras iniciales

Entre las configuraciones más destacadas aparece una muestra de ingeniería con 192 núcleos y 384 hilos funcionando a 4,02 GHz, acompañada de memoria DDR5 en configuración de 8 módulos de 64 GB a 8.000 MT/s, lo que evidencia un enfoque claro hacia cargas de trabajo altamente paralelizables en entornos profesionales y centros de datos de gran escala.

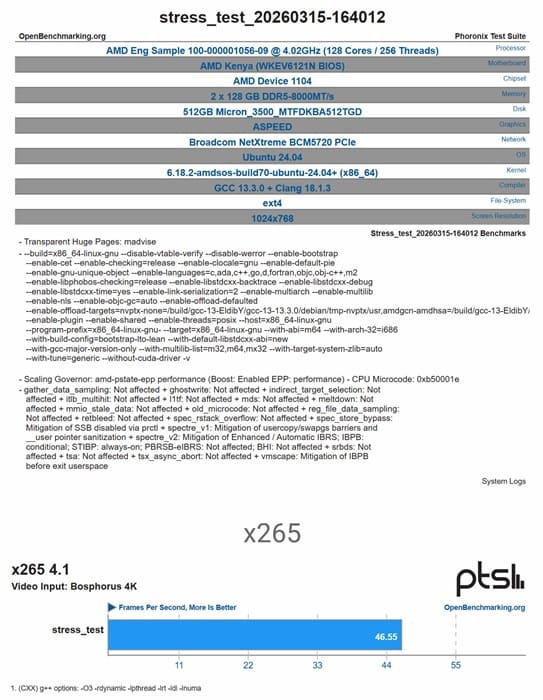

También se han detectado variantes más contenidas, como modelos de 64 núcleos y 128 hilos, lo que indica que la gama Venice cubrirá distintos segmentos dentro del mercado empresarial. Estas pruebas se han realizado en herramientas como 7-Zip, permitiendo obtener una primera referencia de rendimiento, aunque al tratarse de muestras preliminares, los resultados finales serán previsiblemente superiores en versiones comerciales.

Plataforma Socket SP7 y memoria DDR5 como base del salto generacional

Las pruebas realizadas en distintas placas muestran el uso de la nueva plataforma Socket SP7, acompañada de configuraciones de memoria muy amplias. En algunos casos, como en sistemas dual socket, se han utilizado hasta 32 módulos de 64 GB DDR5 a 8.000 MT/s, lo que supone una capacidad total cercana a 2 TB de memoria, un dato especialmente relevante para IA, análisis de datos y virtualización.

Este salto en capacidad y ancho de banda permite a AMD posicionar Venice como una solución orientada a cargas modernas. En este sentido, la combinación de alto número de núcleos y gran capacidad de memoria permite ejecutar cargas masivas sin cuellos de botella, algo clave en entornos donde la eficiencia global del sistema es tan importante como la potencia del procesador.

Diseño modular con CCD e IOD para mejorar la escalabilidad

Otro aspecto relevante es la configuración interna del chip, que sigue apostando por un diseño modular basado en CCD (Core Complex Die) e IOD (Input Output Die). En los modelos más avanzados, se observa una distribución de hasta 8 CCD acompañados de 2 IOD, lo que permite escalar el número de núcleos manteniendo una estructura eficiente y flexible en distintos niveles de rendimiento.

En plataformas dual-socket, esta configuración se duplica, lo que permite escalar el número de núcleos y la capacidad de procesamiento en centros de datos. Este enfoque modular es clave en la estrategia de AMD, ya que permite adaptar el diseño del silicio a distintos niveles de rendimiento sin rediseñar la arquitectura completa, manteniendo eficiencia y flexibilidad.

Rendimiento preliminar cercano a EPYC Turin pese a ser muestras iniciales

A pesar de tratarse de muestras de ingeniería, los primeros resultados indican que los EPYC Venice ya alcanzan un rendimiento similar a modelos equivalentes de la generación Turin, lo que resulta especialmente relevante teniendo en cuenta que no se trata de silicio final ni optimizado para producción, por lo que aún existe margen de mejora en versiones comerciales.

AMD ha adelantado que esta nueva generación ofrecerá mejoras de hasta un 70% en rendimiento y eficiencia junto a un aumento del 30% en densidad, lo que anticipa un salto notable en capacidad de cómputo y eficiencia energética en centros de datos. Además, estos procesadores estarán acompañados por aceleradores de IA dentro de plataformas como Helios, reforzando su papel en el sector.

Vía: Wccftech