AMD está preparando su sexta generación de procesadores EPYC «Venice» para servidores y centros de datos, construida sobre los nuevos núcleos Zen 6 y Zen 6C, y fabricada con el primer nodo de clase 2 nm de TSMC. Filtraciones recientes apuntan a un salto considerable en escalabilidad, caché y capacidad de memoria, todo ello orientado a cargas de trabajo críticas.

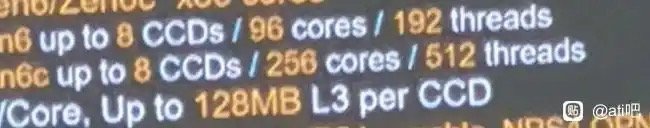

La configuración estándar Zen 6 contará con hasta ocho Core Complex Dies (CCDs) por socket, cada uno con 12 núcleos tradicionales, lo que supone un máximo de 96 núcleos y 192 hilos por procesador. Cada CCD integraría 128 MB de caché L3 compartida, duplicando la cantidad vista en la generación anterior y permitiendo alcanzar 1 TB de caché L3 en un CPU Venice totalmente equipado.

Zen 6C: eficiencia extrema con hasta 512 hilos

Para quienes necesiten densidad extrema de hilos, AMD ofrecerá variantes Zen 6C, con un diseño más compacto que permite alojar hasta 256 núcleos y 512 hilos por socket. Cada núcleo Zen 6C mantendría 2 MB de caché L3 individual, buscando equilibrar latencia y escalabilidad incluso en entornos con cargas masivas de hilos.

Memoria y TDP a gran escala

Venice supondrá un gran avance también en memoria: se espera compatibilidad con DDR5 en configuraciones de 16 canales (SP7) y 12 canales (SP8), pudiendo alcanzar hasta 6 TB de RAM por socket. Aunque aún no se confirma la cifra total de líneas PCIe 5.0, podría superar ampliamente las 128 de la generación anterior.

El consumo térmico variará según el socket: los modelos SP7 llegarían a un TDP de 600W, frente a los 400W de Zen 5, mientras que los SP8 se limitarían a 350-400W, ideales para racks de densidad media.

Lanzamiento estimado para 2025-2026

Este enfoque escalonado permitirá a hiperescaladores y grandes centros de datos adaptar su infraestructura a distintos niveles de potencia y eficiencia. El lanzamiento de la familia EPYC Venice está previsto para finales de 2025 o principios de 2026, marcando un nuevo hito en rendimiento para entornos de misión crítica.

Vía: TechPowerUp