El sector de CPU para centros de datos se prepara para un salto generacional de gran calado. AMD ha desvelado en CES 2026 los primeros detalles técnicos de EPYC Venice, su próxima generación de procesadores para servidores basada en la nueva arquitectura Zen 6, y el análisis del silicio confirma una estrategia clara: más núcleos, chiplets más grandes y un subsistema de entrada y salida profundamente reforzado.

EPYC Venice se convierte además en el primer procesador de centro de datos del mundo fabricado en 2 nm, utilizando el proceso N2P de TSMC. AMD promete más de un 70% de mejora combinada en rendimiento y eficiencia, junto a un aumento superior al 30% en densidad de hilos, situando a esta familia como un pilar clave para cargas masivas de computación, IA e infraestructura cloud.

Zen 6C: el CCD se hace enorme y duplica núcleos

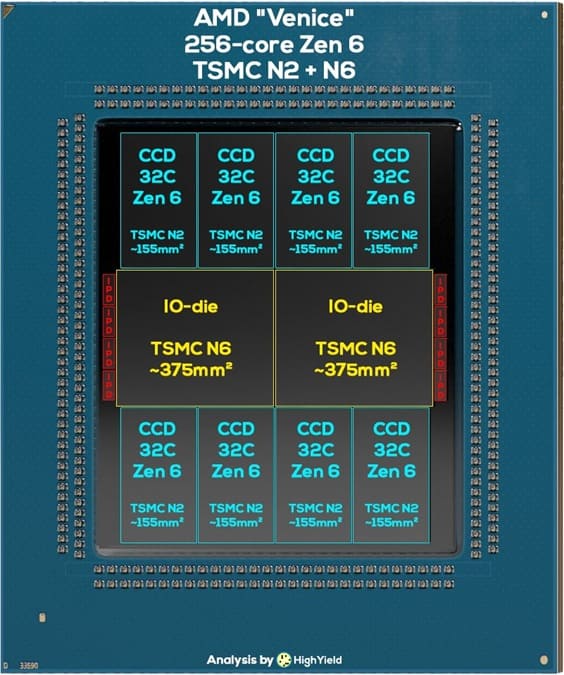

El verdadero protagonista de EPYC Venice es el nuevo CCD Zen 6C. Cada chiplet integra 32 núcleos Zen 6C, el doble frente a los 16 núcleos de Zen 5C, manteniendo el enfoque de alta densidad para servidores. Este salto no es gratuito: el tamaño del die pasa de ~85 mm² en Zen 5C a ~155 mm² en Zen 6C, lo que supone un incremento del 82,3% generación a generación.

Este aumento viene acompañado de una mejora sustancial en caché. Cada CCD Zen 6C incorpora 128 MB de L3, permitiendo alcanzar hasta 1.024 MB de caché L3 total en las configuraciones completas del procesador. Todo ello se fabrica en 2 nm (N2P), frente a los 3 nm N3E utilizados en la generación anterior, lo que explica la combinación de más transistores, más núcleos y mayor eficiencia.

En paralelo, AMD mantendrá CCD Zen 6 estándar, orientados a equilibrio entre frecuencia y latencia, con 12 núcleos y 48 MB de L3 por chiplet, destinados a variantes menos densas pero con mayor rendimiento por núcleo.

Hasta 256 núcleos y dos IO dies de gran tamaño

Las configuraciones más ambiciosas de EPYC Venice (serie EPYC 9006) alcanzarán hasta 256 núcleos y 512 hilos, empleando 8 CCD Zen 6C junto a dos IO dies independientes. Este es otro de los grandes cambios frente a generaciones previas: cada IOD mide ~375 mm² y se fabrica en 6 nm, sumando 750 mm² dedicados exclusivamente a I/O.

En comparación, EPYC Turin utilizaba un único IO die de ~426 mm². El paso a dos IODs indica una ampliación masiva de capacidades, incluyendo controladores de memoria, PCIe, interconexión interna y aceleradores específicos para IA y movimiento de datos, claves en entornos de hyperscale.

AMD refuerza así una de las áreas más críticas del diseño moderno de CPU para servidores: el equilibrio entre cómputo, memoria y conectividad, evitando cuellos de botella en plataformas con decenas o cientos de núcleos activos.

Venice frente a Turin: el salto generacional en cifras

Las diferencias entre generaciones quedan claras al comparar Venice con Turin:

- EPYC 9006 Venice (Zen 6C): 256 núcleos / 512 hilos, hasta 8 CCD, 1.024 MB de L3

- EPYC 9005 Turin (Zen 5C): 192 núcleos / 384 hilos, hasta 12 CCD, 384 MB de L3

En variantes Zen 6 “no C”, Venice ofrecerá 96 núcleos y 192 hilos, manteniendo la misma cifra de caché L3 que Turin, pero con mejoras claras en eficiencia y diseño interno.

Este enfoque modular permite a AMD ajustar densidad, consumo y rendimiento según el perfil del cliente, desde cloud generalista hasta cargas de IA, bases de datos en memoria o simulación científica.

Venice IOD: ~375mm² N6 x 2

Turin IOD: ~426mm² N6 x 1Zen6c CCD: 32 Cores = ~155mm² N2

Zen5c CCD: 16 Cores = ~85mm² N3E https://t.co/n4GJGNWqlo— Hassan Mujtaba (@hms1193) January 12, 2026

Preparados para competir con Intel Diamond Rapids

EPYC Venice llegará al mercado en 2026, dentro de la plataforma SP7, y competirá directamente con los futuros procesadores Intel Diamond Rapids, basados en el nodo 18A. Con soporte previsto para DDR5 de muy alta velocidad, hasta 16 canales de memoria y PCIe Gen 6, AMD deja claro que la próxima batalla en el sector de CPU para centros de datos se librará tanto en silicio de CPU como en capacidad de I/O y escalabilidad.

Con Zen 6C, 2 nm, 256 núcleos y dos IO dies masivos, EPYC Venice representa uno de los diseños más ambiciosos jamás realizados por AMD, y marca el camino de cómo serán los procesadores de alto rendimiento en la segunda mitad de la década.

Vía: Wccftech