Un equipo de la Peking University y la Chinese Academy of Sciences ha desarrollado el que describen como el transistor ferroeléctrico más pequeño del mundo, con una longitud de puerta de 1 nm y funcionamiento estable a solo 0,6 V. El avance, publicado en Science Advances, aborda un problema estructural del sector de semiconductores: la incompatibilidad de voltaje entre lógica y memoria no volátil.

En los chips actuales, la lógica digital moderna opera en torno a 0,7 V, mientras que memorias como la NAND flash requieren 5 V o más para escritura. Incluso generaciones previas de transistores de efecto de campo ferroeléctrico (FeFET) superaban los 1,5 V, obligando a integrar circuitos de bombeo de carga que incrementan el consumo energético, el área de silicio de GPU o CPU dedicada a memoria y la complejidad de diseño. En arquitecturas de IA, entre el 60% y el 90% del consumo total se destina únicamente al movimiento de datos, no al cálculo.

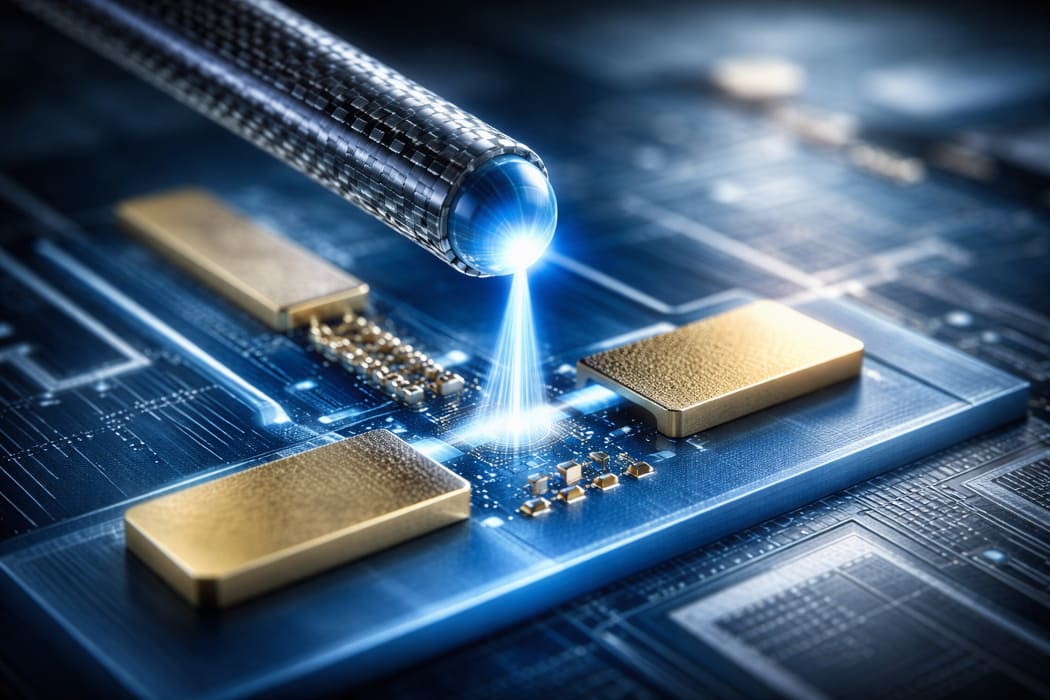

Nanopuerta basada en nanotubos de carbono

El equipo, liderado por Qiu Chenguang y Peng Lianmao, utilizó nanotubos de carbono metálicos de pared simple como electrodos de puerta. Esta arquitectura actúa como una nanopunta conductora, concentrando el campo eléctrico local y mejorando el acoplamiento ferroeléctrico entre la capa activa y el canal.

Gracias a esta intensificación, el dispositivo puede cambiar su estado de polarización con solo 0,6 V, por debajo del voltaje lógico estándar, manteniendo además inmunidad frente a los efectos de canal corto, un fenómeno crítico cuando la longitud de canal se reduce a escala nanométrica. Este punto es clave para evitar degradación eléctrica en nodos extremos.

MoS₂, relación de corriente on/off de 2 millones y 1,6 ns

Los dispositivos fabricados, basados en disulfuro de molibdeno (MoS₂), presentan una relación de corriente on/off de 2 millones, junto con una velocidad de programación de 1,6 ns. Estas métricas indican una combinación sólida de retención de datos, rapidez de escritura y estabilidad eléctrica, elementos fundamentales para integración en arquitecturas avanzadas.

Al lograr compatibilidad directa entre memoria no volátil y lógica, se elimina la necesidad de circuitos de elevación de tensión, reduciendo pérdidas energéticas y simplificando la arquitectura del chip. Esto podría facilitar interacciones de datos de alta velocidad sin penalización térmica adicional.

Implicaciones para IA, inteligencia en el borde y dispositivos wearables

Según los investigadores, el principio físico empleado es aplicable a materiales ferroeléctricos convencionales y compatible con procesos industriales estándar, lo que abre la puerta a su adopción futura. El avance tiene especial relevancia para inferencia de modelos de gran tamaño, inteligencia en el borde y dispositivos wearables, donde la eficiencia energética es determinante.

Si la escalabilidad industrial confirma los resultados experimentales, este transistor de 1 nm y 0,6 V podría convertirse en una pieza clave para próximas generaciones de chips de IA energéticamente optimizados, acercando definitivamente la memoria no volátil al dominio eléctrico de la lógica moderna.

Vía: NotebookCheck