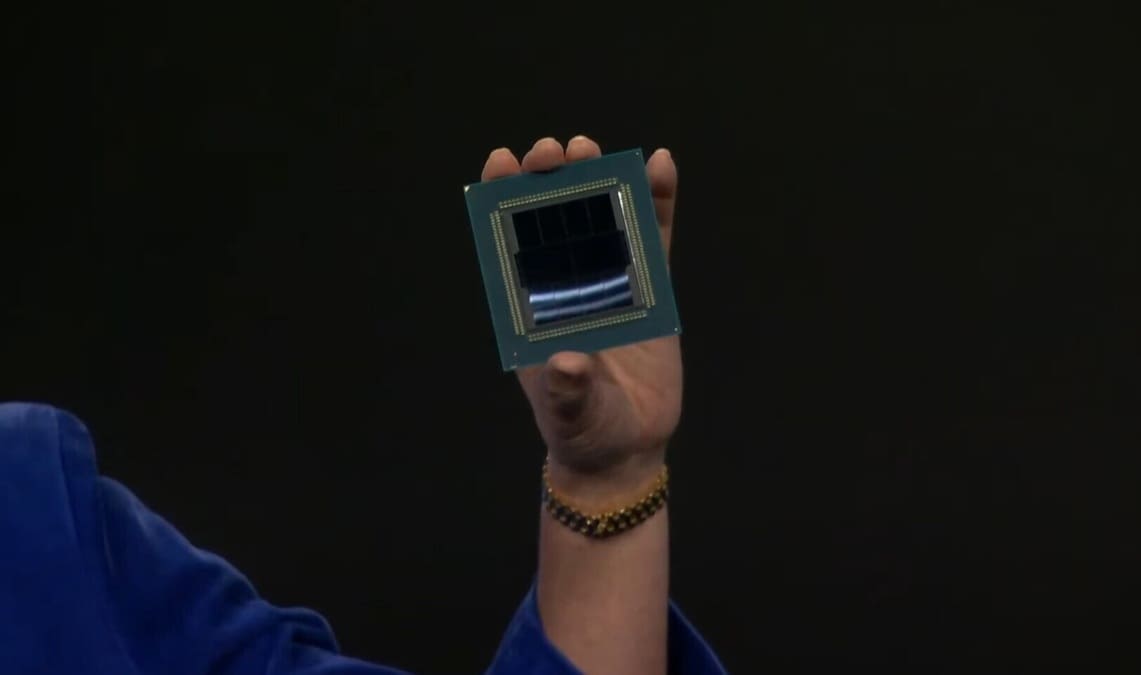

Durante el evento de CES 2026, AMD ha ofrecido un primer adelanto de su próxima generación de procesadores empresariales EPYC “Venice”, de la mano de su CEO, Lisa Su. El anuncio sitúa a Venice como una pieza clave dentro de la infraestructura de IA y cómputo acelerado de la compañía para 2026, actuando como el procesador central de los nuevos racks Helios, diseñados para cargas masivas de entrenamiento e inferencia.

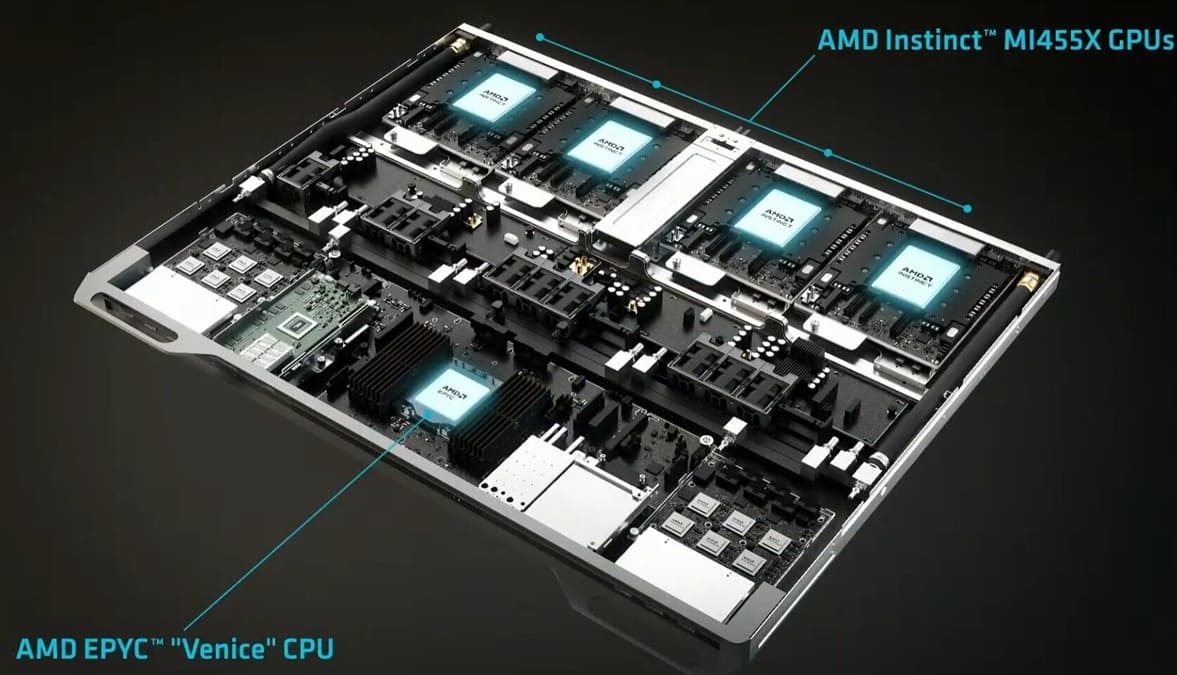

Cada nodo de estos racks Helios combina cuatro GPUs AMD MI455X con un único procesador EPYC Venice, configurado con nada menos que 256 núcleos y 512 hilos. Esta cifra marca un salto sustancial frente a la generación actual y deja claro que AMD apunta directamente al segmento de centros de datos de alto rendimiento, donde la densidad de cómputo por nodo es crítica.

Un diseño chiplet radicalmente distinto

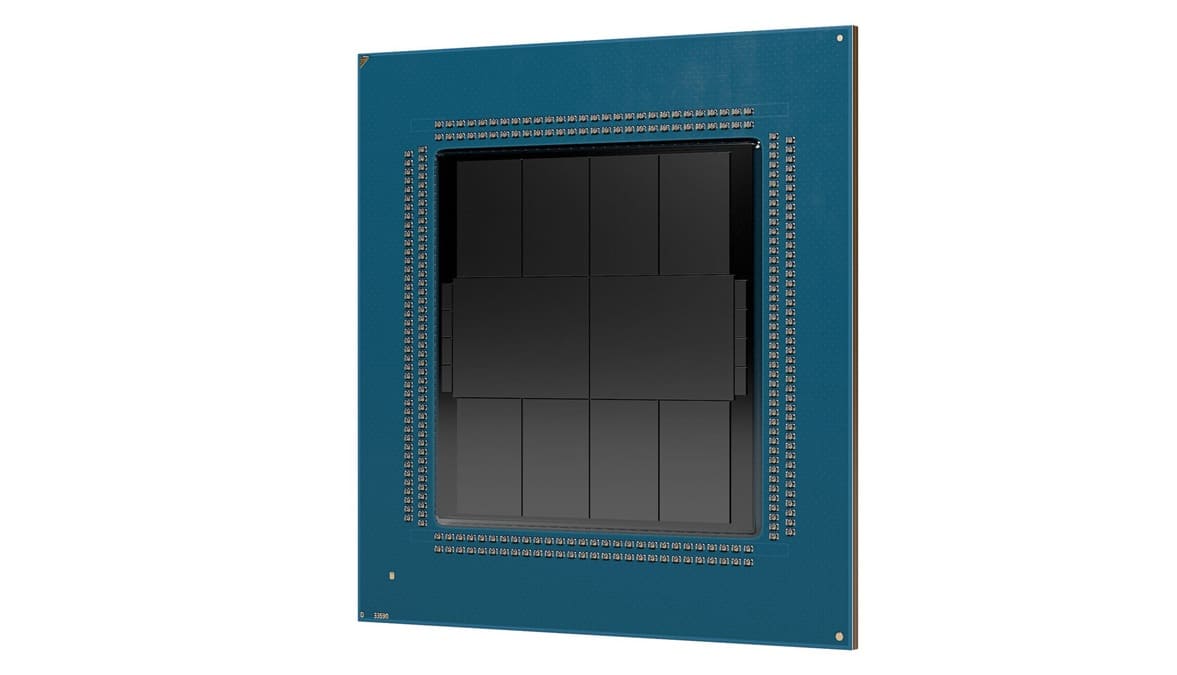

Uno de los aspectos más llamativos de EPYC Venice es su nuevo diseño de chiplets, claramente diferenciado de las generaciones anteriores. En lugar del esquema tradicional, el paquete integra dos I/O dies de servidor centralizados, fabricados en 4 nm, flanqueados a ambos lados por hasta ocho CCDs.

Cada uno de estos CCDs está fabricado en 2 nm y aloja 32 núcleos Zen 6, lo que explica cómo AMD alcanza la cifra total de 256 núcleos en un solo Socket. Este planteamiento no solo incrementa la densidad, sino que también optimiza la comunicación interna y la escalabilidad del diseño.

Por ahora, AMD no ha confirmado si estos núcleos corresponden a Zen 6 completos, capaces de mantener frecuencias elevadas, o a variantes Zen 6c, que comparten ISA e IPC, pero operan a relojes más contenidos. En cualquier caso, el enfoque está claramente orientado a máximo paralelismo y eficiencia en cargas de servidor.

Memoria, I/O y soporte para IA a gran escala

El subsistema de memoria de EPYC Venice también da un paso adelante importante. El procesador incorpora una interfaz de memoria DDR5 de 16 canales, dividida en 32 subcanales, una configuración que explica la necesidad de desagregar el I/O die en dos chips independientes, unidos mediante un tejido de interconexión de alta velocidad.

Además, AMD planea un aumento notable en el número de líneas PCIe y CXL frente a la generación actual. Este incremento es clave para alimentar correctamente los cuatro aceleradores MI455X, así como DPUs, NICs de 800G y otros dispositivos de alto ancho de banda que forman parte del ecosistema de los racks Helios.

EPYC Venice como pilar de Helios

Con EPYC Venice, AMD refuerza su estrategia de plataformas completas, donde CPU y GPU están pensadas para trabajar de forma conjunta dentro de un mismo nodo. Los racks Helios, impulsados por MI455X y Zen 6, apuntan directamente a competir en el segmento más exigente del mercado de IA empresarial, HPC y cloud a gran escala.

Aunque todavía faltan detalles sobre frecuencias finales, consumo y configuraciones comerciales, este primer adelanto deja claro que AMD prepara uno de los saltos arquitectónicos más ambiciosos de su historia en el sector de servidores. EPYC Venice no solo aumenta el recuento de núcleos, sino que redefine la arquitectura interna para adaptarse a la nueva era de la IA acelerada.

Vía: TechPowerUp