El sector de los procesadores para centros de datos empieza a perfilar uno de los saltos arquitectónicos más importantes de Intel en los últimos años. Nuevos parches detectados en el kernel de Linux han revelado detalles clave de los futuros Intel Diamond Rapids Xeon, una familia de CPUs que apostará por una arquitectura multi-tile aún más modular que la vista hasta ahora en la gama Xeon.

La gran novedad es la introducción de dos tipos de tiles completamente diferenciados, diseñados para separar de forma clara el cómputo del subsistema de entrada/salida y memoria, una decisión que marca distancias frente a generaciones anteriores.

CBB e IMH: una separación total de funciones

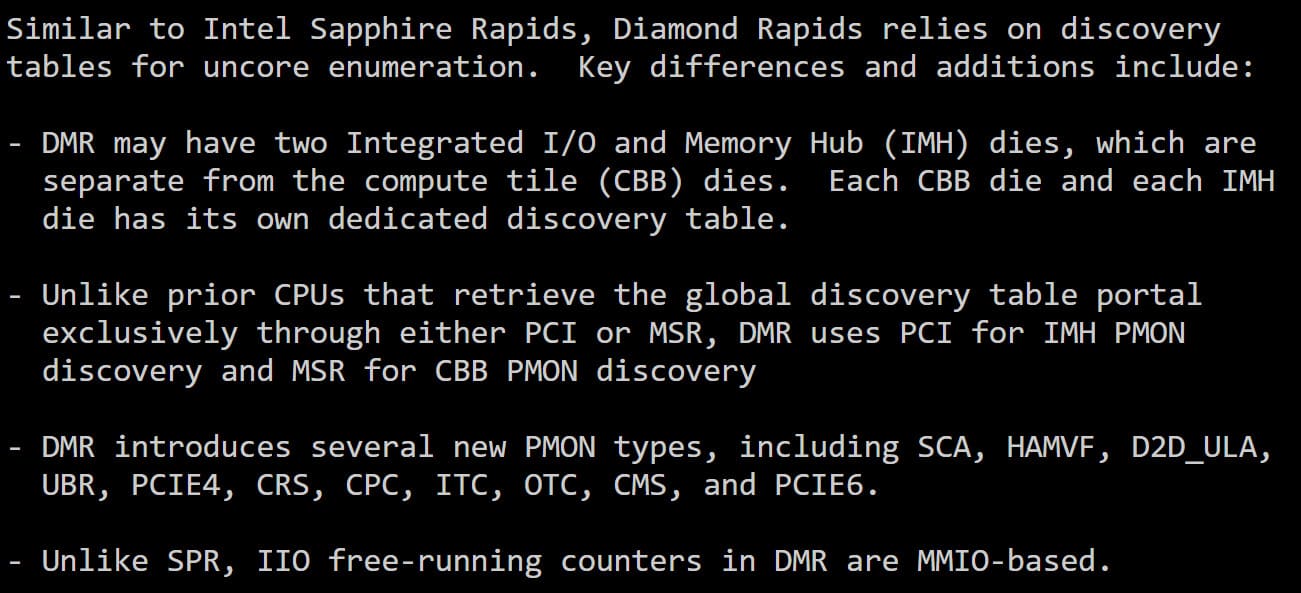

En Diamond Rapids, Intel introducirá el nuevo tile CBB (Core Building Block), que actuará como bloque de cómputo principal. A diferencia de Granite Rapids, donde el controlador de memoria integrado (IMC) convivía dentro del mismo tile, esta generación dará un paso más en la desagregación.

El IMC, junto con las funciones de entrada/salida, se trasladará a un tile independiente denominado IMH (Integrated I/O & Memory Hub). Este enfoque permite una mayor flexibilidad en el diseño, facilitando escalar el número de controladores de memoria y líneas PCIe sin penalizar el área dedicada a núcleos.

Según la información compartida por @InstLatX64, Diamond Rapids podría integrar hasta dos tiles IMH, los cuales estarían situados sobre el base tile, siguiendo una filosofía similar a la empleada por Clearwater Forest.

Preparados para PCIe Gen6 y plataformas de nueva generación

Otro dato relevante que aparece en los parches es la compatibilidad con PCIe Gen6, una tecnología llamada a convertirse en el nuevo estándar del sector de servidores y centros de datos a partir de 2026. Este soporte encaja con la hoja de ruta conocida de Intel, que ya había confirmado la llegada de PCIe Gen6 a plataformas de próxima generación como Diamond Rapids y Venice.

La adopción de PCIe Gen6 permitirá mayor ancho de banda por línea, algo crítico en entornos de IA, HPC y almacenamiento de alto rendimiento, donde la conectividad es tan importante como la potencia de cálculo.

Insightful Linux kernel patch:#Intel #DiamondRapids CPU chip = Core Building Block (CBB) and unlike #GNR they do not have an IMC.#DMR can have a chip with two "Integrated I/O and one memory hub (IMH)".

DMR goes even further than #CWF the IMC is on the Base Tile.

1/2 pic.twitter.com/0jHPUD3hJX— InstLatX64 (@InstLatX64) January 2, 2026

Hasta 192 núcleos… o incluso más

En cuanto a configuración, los Diamond Rapids Xeon están previstos para alcanzar hasta 192 núcleos, aunque algunos rumores apuntan a variantes que podrían llegar a los 256 núcleos, sin confirmación oficial por parte de Intel hasta la fecha.

Estos procesadores utilizarán el nodo de fabricación 18A, uno de los más avanzados de la compañía, y estarán basados en la nueva arquitectura Panther Cove P-Cores, diseñada para maximizar el rendimiento por núcleo en cargas empresariales y de computación intensiva.

TDP extremos y enfoque claramente profesional

Los primeros datos de plataforma apuntan a cifras muy elevadas de consumo. Diamond Rapids se desplegará sobre el Socket LGA 9324, con soporte multi-socket, y se habla de TDPs de hasta 650W, lo que deja claro que estamos ante CPUs pensadas exclusivamente para servidores de alto nivel y centros de datos, no para entornos convencionales.

Este enfoque permite a Intel competir de tú a tú en segmentos donde el rendimiento absoluto, la escalabilidad y la densidad de cómputo son prioritarios frente al consumo energético.

Lanzamiento previsto para 2026

Si se cumple la hoja de ruta actual, Intel planea introducir los Diamond Rapids Xeon a mediados o en la segunda mitad de 2026. Para entonces, el mercado del centro de datos estará plenamente inmerso en la transición a PCIe Gen6, memorias de nueva generación y plataformas diseñadas específicamente para IA y cargas masivas de datos.

Con Diamond Rapids, Intel deja claro que su futuro en el sector Xeon pasa por una arquitectura profundamente modular, capaz de adaptarse mejor a distintos escenarios profesionales y de escalar con mayor eficiencia que las generaciones anteriores.

Vía: Wccftech