Apple lanzó los A19 Pro y A19 hace algo más de tres meses como el corazón de la nueva generación de iPhone 17, incluido el ultradelgado iPhone Air. Ambos SoCs de 3 nm y 64 bits basados en arquitectura Arm han despertado un notable interés técnico, especialmente tras la aparición de las primeras imágenes detalladas del silicio del A19 Pro procedentes de análisis independientes a mediados de noviembre.

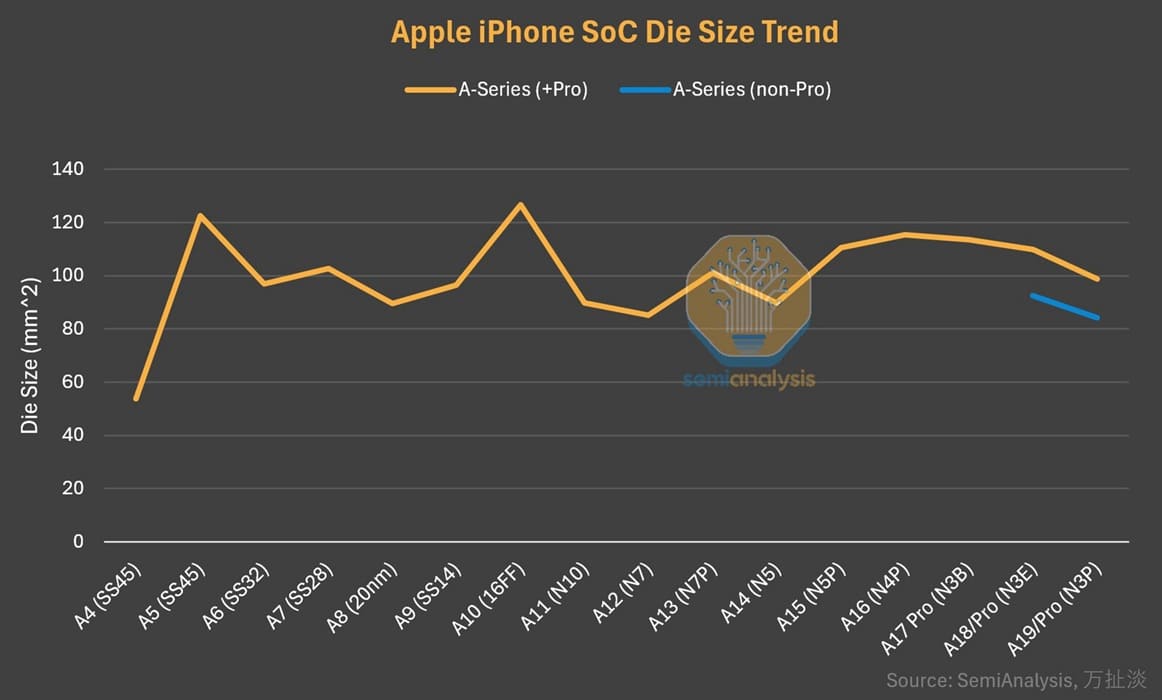

Las investigaciones se han centrado en la adopción por parte de Apple del proceso N3P de TSMC, una variante de alto rendimiento dentro de la familia de nodos de 3 nm, que supone un salto frente al N3E (FinFET) utilizado en los A18 Pro y A18. El cambio no solo afecta al rendimiento y la eficiencia, sino también al tamaño físico del chip, un factor clave en diseño móvil avanzado.

Comparativa directa: A19 Pro frente a A18 Pro

Los análisis detallados revelan que el A19 Pro presenta una reducción del 10% en superficie, pasando de 105 mm² en el A18 Pro a 98,6 mm² en el nuevo modelo. En el caso del A19 estándar, la reducción frente al A18 se sitúa en torno al 9%, según estimaciones de SemiAnalysis.

Este dato resulta especialmente llamativo, ya que el propio salto de N3E a N3P solo explicaría alrededor de un 4% de reducción de área. La conclusión es clara: Apple no se ha limitado a cambiar de nodo, sino que ha llevado a cabo optimizaciones internas profundas para lograr una contracción mucho más significativa del silicio.

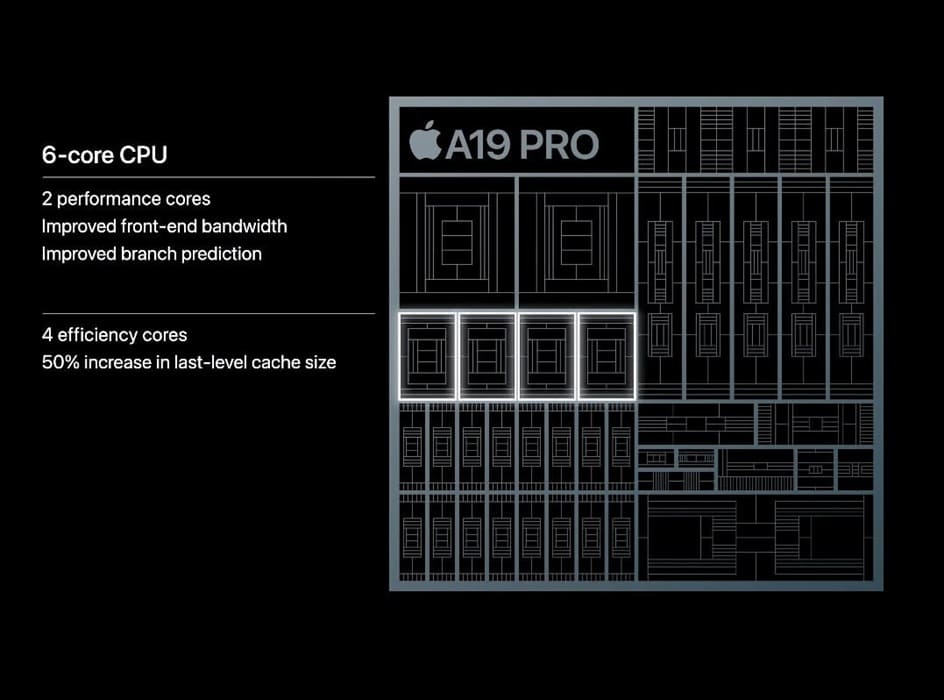

Cambios internos clave en CPU, GPU y caché

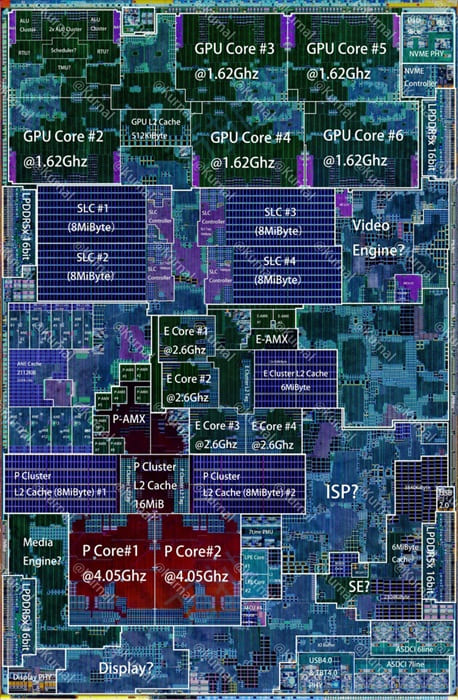

SemiAnalysis destaca varias modificaciones relevantes en la microarquitectura del A19 Pro. En el análisis por bloques, el núcleo de alto rendimiento (P-Core) se ha reducido aproximadamente un 4%, mientras que los E-Core y la GPU crecen alrededor de un 10%, reflejando un mayor presupuesto de transistores destinado a mejorar la eficiencia y el rendimiento, algo que ya se ha dejado notar en los benchmarks.

Otro punto clave está en la caché del sistema. El macro de caché ha duplicado su tamaño hasta 32 KB, logrando una densidad un 10% superior. A igualdad de capacidad total de 4 MB de SLC, el A18 ocupaba 1,08 mm², mientras que el A19 reduce esta cifra a 0,98 mm², una mejora notable en términos de eficiencia de diseño.

Optimización del área “uncore” y resultado final

Más allá de CPU y GPU, Apple también ha refinado la disposición del área uncore del SoC, que engloba bloques como el motor de pantalla, media engine, ISP, seguridad y otros elementos auxiliares. Una distribución más eficiente de estos componentes ha contribuido de forma decisiva al recorte global de superficie.

Según SemiAnalysis, la combinación de mejoras de diseño, redistribución de transistores y el uso del nodo N3P ha permitido a Apple alcanzar “una reducción de área comparable a la de un cambio de nodo mayor”, algo poco habitual en una sola generación. El resultado es un chip más pequeño, pero también más potente y eficiente, un logro técnico relevante incluso dentro del contexto altamente optimizado del silicio móvil de Apple.

En conjunto, el A19 Pro confirma que la evolución de los SoCs de Apple ya no depende únicamente del proceso de fabricación, sino de una ingeniería interna cada vez más sofisticada, capaz de exprimir cada milímetro cuadrado de silicio para mantener su ventaja competitiva.

Vía: TechPowerUp