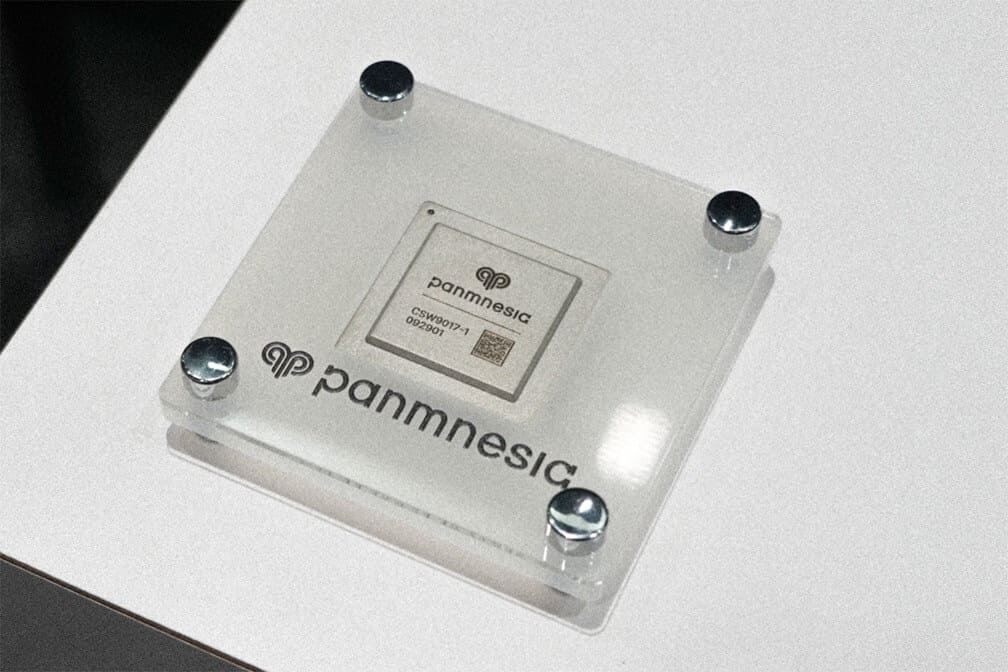

Panmnesia ha anunciado la disponibilidad de muestras de su nuevo Fabric Switch PCIe 6.0/CXL 3.2, el primero del sector en ofrecer soporte completo para enrutamiento basado en puertos (PBR). Este avance marca un paso clave hacia arquitecturas de computación componible, optimizadas para cargas de trabajo de inteligencia artificial (IA) y computación de alto rendimiento (HPC).

El nuevo conmutador es una solución híbrida que combina en un solo chip compatibilidad con PCIe Gen 6 y CXL 3.2, manteniendo además retrocompatibilidad total con todas las generaciones anteriores de ambos estándares. Implementado según las especificaciones oficiales de PCIe 6.0 y CXL 3.2, garantiza una interoperabilidad completa y un funcionamiento estable en entornos heterogéneos.

Arquitectura componible y doble modo de enrutamiento

Una de las principales novedades es la capacidad del switch para operar tanto en modo PBR (Port-Based Routing) como en modo HBR (Hierarchy-Based Routing). Gracias a esta flexibilidad, los integradores pueden adaptar la topología de red según las necesidades de rendimiento o escalabilidad, permitiendo crear infraestructuras dinámicas que funcionan como un único acelerador distribuido.

El diseño interno se apoya en el controlador PCIe/CXL propietario de Panmnesia, que optimiza las rutas de comunicación para minimizar la latencia y mejorar la coherencia de caché entre dispositivos. Esto permite conectar miles de unidades —como GPUs, CPUs o aceleradores de memoria— a través de una malla unificada, sin depender de configuraciones manuales ni jerarquías estáticas.

Comunicación acelerada y latencias ultra bajas

El Fabric Switch alcanza tasas de transferencia de 64 GT/s propias del estándar PCIe Gen 6, acelerando el intercambio de grandes volúmenes de datos entre dispositivos interconectados. Además, ofrece soporte completo para los subprotocolos CXL.cache, CXL.mem y CXL.io, garantizando coherencia de memoria entre nodos y eliminando copias redundantes.

Panmnesia afirma que su arquitectura de alta dispersión (high fan-out) reduce el número de saltos necesarios en clústeres, minimizando la latencia total de acceso a datos. El controlador CXL propietario alcanza latencias de decenas de nanosegundos, lo que lo convierte en una de las soluciones más rápidas del mercado para interconexión entre aceleradores.

Escalabilidad y aplicaciones en IA y HPC

El switch está diseñado para escalar a gran escala, pudiendo interconectar miles de dispositivos a través de múltiples racks mediante una topología cascada que mantiene una latencia mínima. Esto resulta especialmente útil en cargas de trabajo intensivas como modelos de lenguaje (LLMs), recomendadores (DLRM) o simulaciones científicas basadas en MPI, donde el acceso rápido a la memoria y la comunicación eficiente entre nodos son críticos.

Disponibilidad

El Panmnesia PCIe 6.0/CXL 3.2 Fabric Switch ya se encuentra disponible para socios de acceso anticipado, que pueden solicitar muestras o sistemas piloto. Además, los controladores PCIe/CXL integrados en el switch están verificados en silicio, y también se ofrecerán como productos independientes para aplicaciones de memoria, CPU y aceleradores.

Vía: TechPowerUp