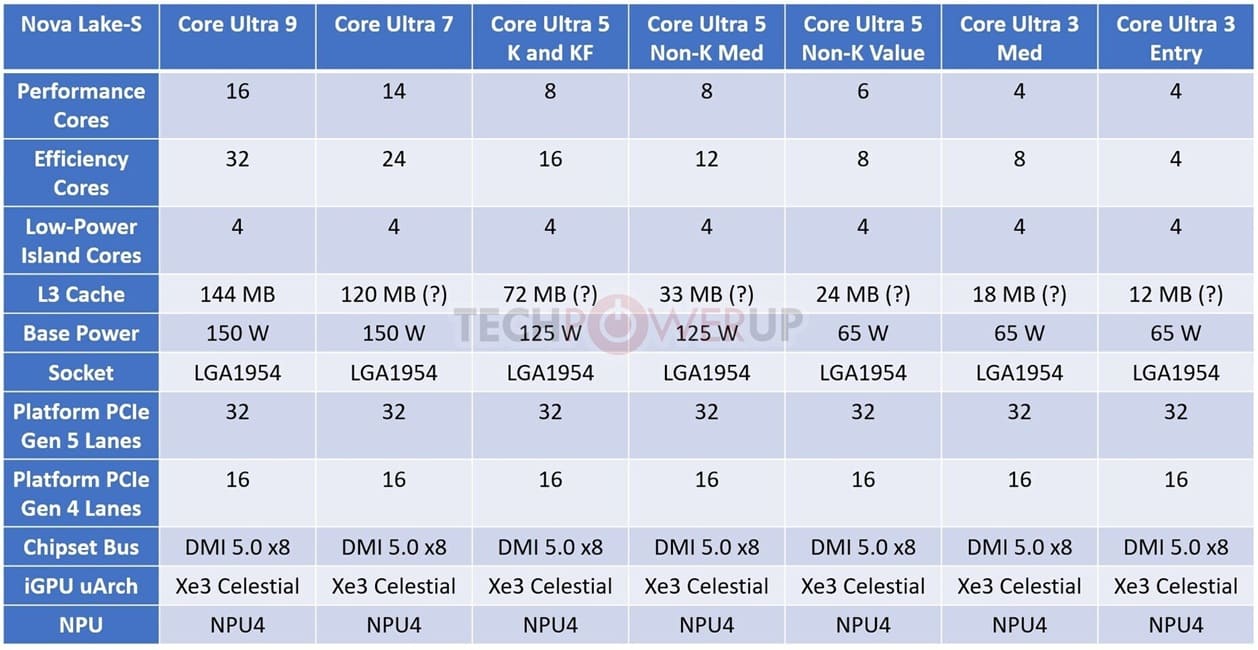

Intel ha revelado detalles clave sobre Nova Lake-S, la variante de escritorio de su próxima generación de procesadores. Esta arquitectura supondrá un gran avance respecto a las actuales, gracias a una configuración máxima de 16P+32E+4LPE, lo que suma 52 núcleos por socket. Estará formada por 16 núcleos “Coyote Cove” de alto rendimiento, 32 núcleos “Arctic Wolf” de eficiencia energética, y 4 núcleos LPE ubicados en una isla de bajo consumo dentro del SoC, una estructura heredada de Meteor Lake.

El modelo insignia, Core Ultra 9, incluirá esta configuración completa y vendrá con una caché L3 de 144 MB, lo que lo posiciona como una opción interesante para cargas exigentes, incluyendo juegos. Tendrá un TDP base de 150W en las variantes desbloqueadas K y KF.

Nuevas configuraciones en las gamas Core Ultra 7, 5 y 3

La gama Core Ultra 7 apostará por una configuración de 14P+24E+4LPE (42 núcleos), desactivando parte de los núcleos del modelo superior. También mantendrá un TDP de 150W en las versiones K y KF.

Por su parte, Core Ultra 5 llegará con tres variantes:

- 8P+16E+4LPE para los modelos K/KF (28 núcleos)

- 8P+12E+4LPE para modelos estándar

- 6P+8E+4LPE para la opción más básica de la serie

Intel no ha confirmado si utilizarán el mismo tile físico del Ultra 9 o un diseño más compacto.

En la gama de entrada, Core Ultra 3 ofrecerá configuraciones de:

- 4P+8E+4LPE (16 núcleos, TDP de 65W)

- 4P+4E+4LPE (12 núcleos, también con 65W)

Plataforma I/O y gráficos integrados

La plataforma Nova Lake-S incluirá hasta 32 líneas PCIe 5.0 y 16 líneas PCIe 4.0, con buses DMI 5.0 que podrían alcanzar el ancho de banda de un PCIe 5.0 x8 en chipsets superiores. También se espera que todos los modelos integren NPUs compatibles con Microsoft Copilot+, asegurando capacidad de aceleración local de IA.

En cuanto a los gráficos integrados, todos los chips contarán con una iGPU basada en la arquitectura Xe3 “Celestial”, aunque con una escala menor respecto a las variantes móviles.

Lanzamiento previsto para 2026

Intel planea lanzar Nova Lake-S en 2026, como parte de su apuesta por mejorar el rendimiento multinúcleo, ampliar las capacidades de IA en local y mantener competitividad frente a los futuros chips de AMD y Apple.

Vía: TechPowerUp