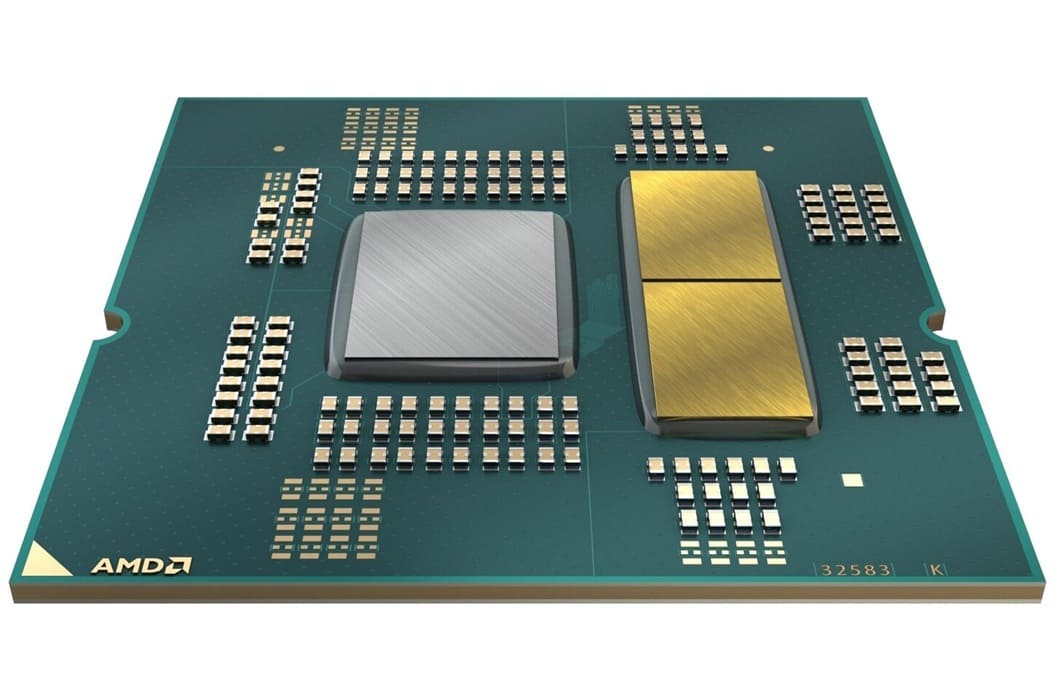

Según documentación compartida con fabricantes de placas base, AMD utilizará los nodos N3 y N2 personalizados de TSMC en su futura generación de CPUs Zen 6, prevista para finales de 2026. El diseño contempla cinco líneas distintas de silicio destinadas a servidores, sobremesas y portátiles, todas ellas con una fuerte orientación al rendimiento y eficiencia térmica.

EPYC Venice: hasta 256 núcleos con interconexión multichip

En el ámbito de servidores, la nueva línea EPYC «Venice» se dividirá en dos variantes: Venice clásico, enfocado a despliegues generales, y Venice denso, dirigido a centros de datos en la nube de alta densidad. Ambos chips estarán fabricados con un nodo N2P personalizado, que ofrece entre un 8 y un 10 % más de frecuencia que el actual N3E.

Cada die Venice clásico integrará 12 núcleos Zen 6, mientras que cada die Venice denso alcanzará los 32 núcleos Zen 6c, permitiendo montar procesadores de hasta 192 o incluso 256 núcleos mediante la interconexión de ocho dies con encapsulado multichip.

Ryzen 10000 y nuevos chips para portátiles

Para el segmento cliente, AMD utilizará nombres clave que reflejan su enfoque:

- Olympic Ridge será la base de los Ryzen 10000 para escritorio, utilizando el nodo N2P de alto rendimiento.

- Gator Range se dirigirá a portátiles gaming de más de 55 W, priorizando el rendimiento bruto.

- Medusa Point cubrirá los portátiles delgados y ligeros, con un diseño híbrido: chip de cómputo en N2P combinado con tile de I/O en N3P.

- Los modelos de entrada, en cambio, apostarán por chips monolíticos en N3P, más económicos y fáciles de producir.

- También figuran en la hoja de ruta variantes como Medusa Halo y Bumblebee, esta última enfocada al mercado más asequible, aunque sus nodos de fabricación aún están por confirmar.

Una integración profunda entre AMD y TSMC

La colaboración entre AMD y TSMC va más allá del simple uso de nodos: ambas compañías están cooptimizando capas metálicas y bibliotecas lógicas, dando lugar a lo que internamente se conoce como un «stack N2-AMD», que va más allá de un nodo N2P estándar.

La primera tanda de silicio estará lista antes de Navidad, con producción en volumen planificada para la campaña de portátiles back-to-school de 2026 y una segunda oleada de servidores poco después.

Vía: TechPowerUp