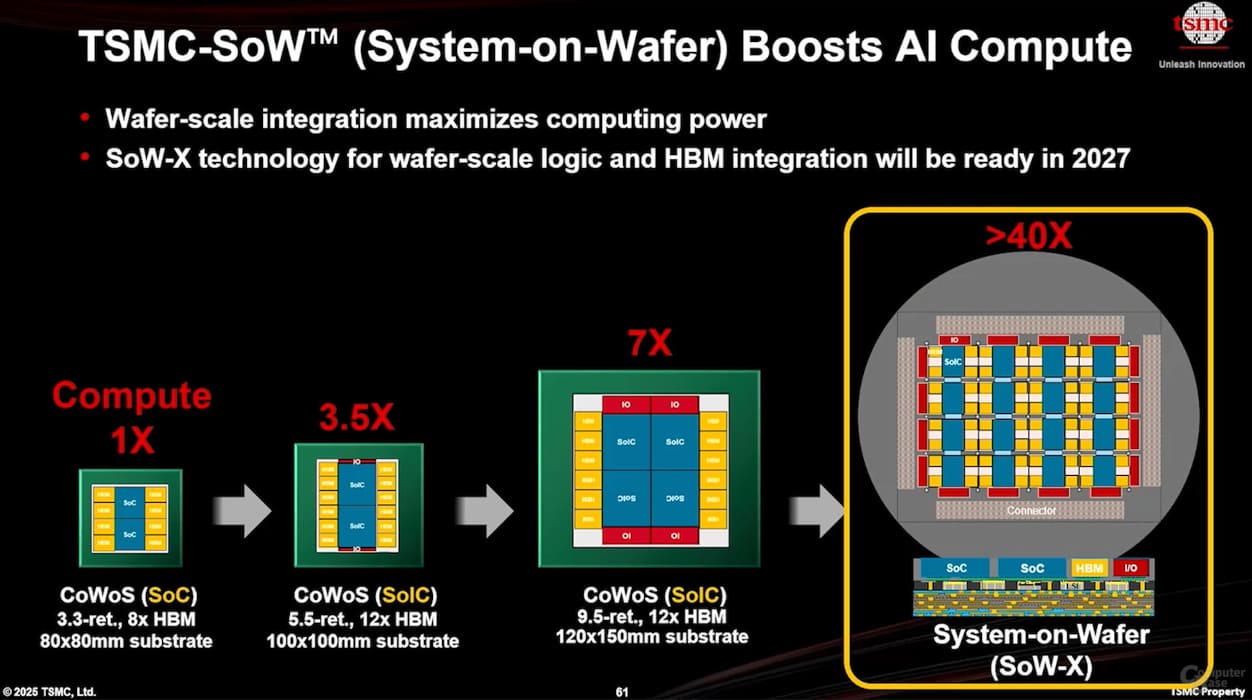

TSMC ha anunciado su nueva tecnología CoPoS (Chips on Panel on Substrate), que representa un hito en el diseño de encapsulados avanzados para computación de alto rendimiento. Frente a las actuales soluciones CoWoS basadas en obleas circulares de 120 × 150 mm, CoPoS permitirá encapsular componentes sobre paneles rectangulares de hasta 310 × 310 mm. Este aumento de área útil —más de cinco veces superior— permitirá integrar múltiples chiplets GPU, apilar hasta 12 módulos HBM4 y combinar I/O de alto ancho de banda, todo en un único sustrato.

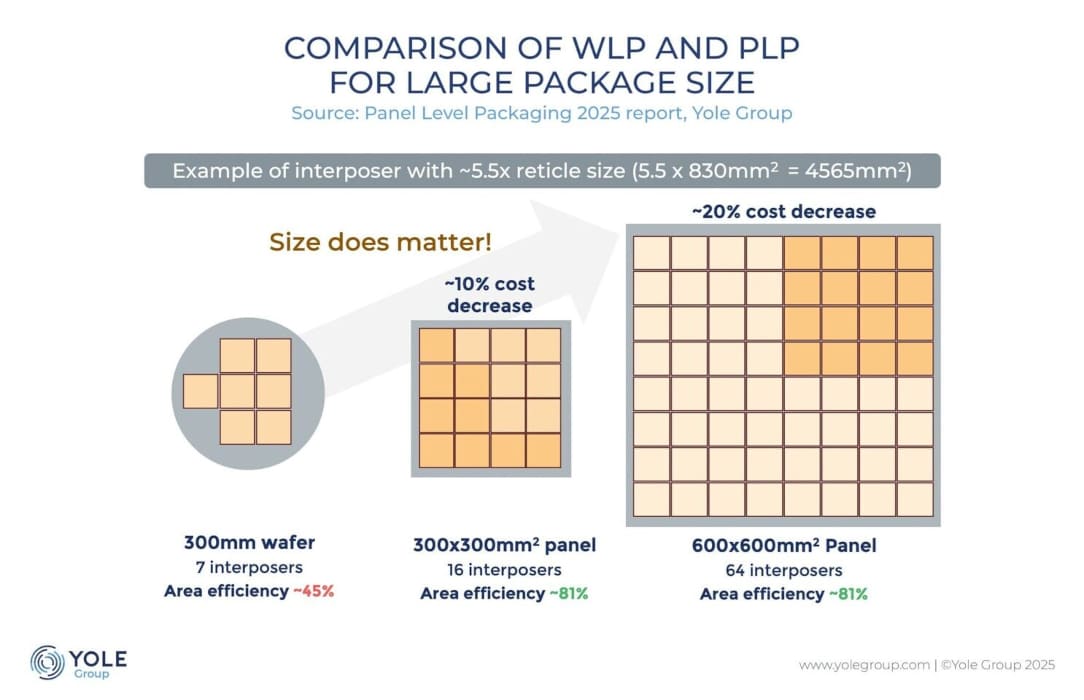

Paneles rectangulares para reducir costes y escalar la producción

El paso de empaquetado a nivel de oblea (WLP) a empaquetado a nivel de panel (PLP) supone una revolución en eficiencia. Los paneles permiten producir más unidades por ciclo con costes menores y mayor velocidad de iteración, lo que resulta clave ante la demanda creciente de soluciones para IA. TSMC instalará su primera línea piloto de CoPoS en 2026, dentro de su filial Visionchip, y espera comenzar la producción en masa entre finales de 2028 y principios de 2029.

El complejo elegido para ello es el campus Chiayi AP7 de TSMC, que también albergará tecnologías como System-on-Wafer y módulos multichip. Este nuevo enfoque, junto a innovaciones como los sustratos de vidrio o la fotónica de silicio, busca resolver los límites térmicos y de espacio de los encapsulados actuales.

NVIDIA, primer cliente con una configuración brutal de GPU + HBM4

NVIDIA será el primer socio de TSMC en implementar CoPoS, aprovechando su gran superficie para incluir hasta 12 chips HBM4 junto a varios chiplets GPU, todo orientado a cargas intensivas de IA. Con ello, pretende superar las limitaciones actuales del diseño modular con CoWoS.

Por su parte, AMD y Broadcom seguirán utilizando las variantes CoWoS-L y CoWoS-R para sus productos de gama alta. Sin embargo, la hoja de ruta de TSMC marca claramente una dirección hacia CoPoS y PLP como estándar dominante para encapsulados complejos de nueva generación.

Si todo va según lo previsto, los primeros dispositivos basados en CoPoS podrían llegar al mercado a finales de 2029, marcando el inicio de una nueva era para la computación de alto rendimiento y la inteligencia artificial.

Vía: TechPowerUp