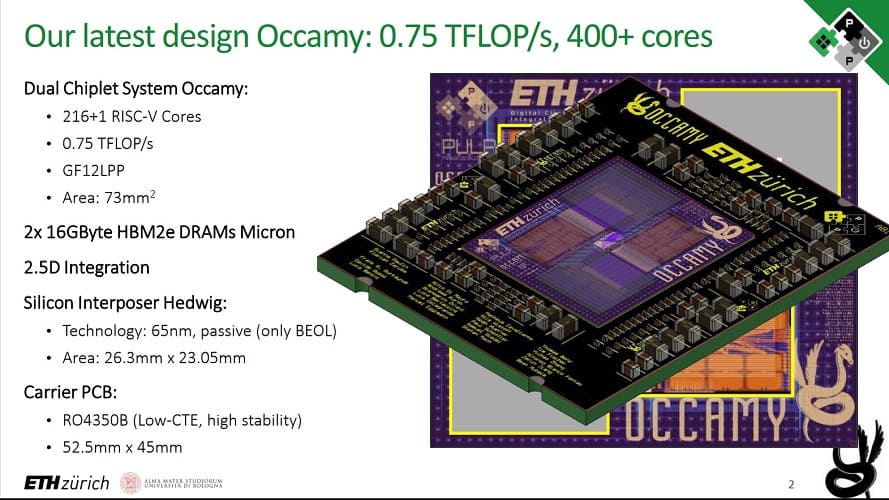

La Agencia Espacial Europea ha formado un grupo con investigadores de ETH Zürich y la Universidad de Bolonia para diseñar y desarrollar un procesador RISC-V destinado a potenciar las capacidades de cálculo en el espacio. La tarea se asignó al proyecto Parallel Ultra Low Power (PULP) Platform, que creó un silicio RISC-V open source con conexiones reales. Denominado Occamy, es un chip de IA de alto rendimiento diseñado para la eficiencia.

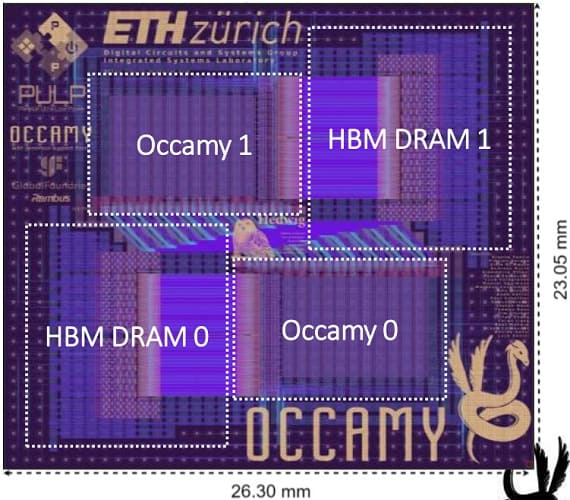

Basado en el proceso de bajo consumo GF12LPP de 12 nm de GlobalFoundries, el diseño del chiplet se coloca sobre un intercalador pasivo de 65 nm. Basado en RISC-V ISA, Occamy utiliza hasta 231 núcleos con una longitud de 32 bits en cada uno de los dos chiplets, lo que suma un total de 432 núcleos de 32 bits. Combinado con unidades de coma flotante de 64 bits (FPUS), el chip Occamy puede alcanzar 0,768 TeraFLOPS en FP64, 1,536 TeraFLOPS en FP32, 3,072 TeraFLOPS en FP16 y 6,144 TeraFLOPS en FP8 de precisión.

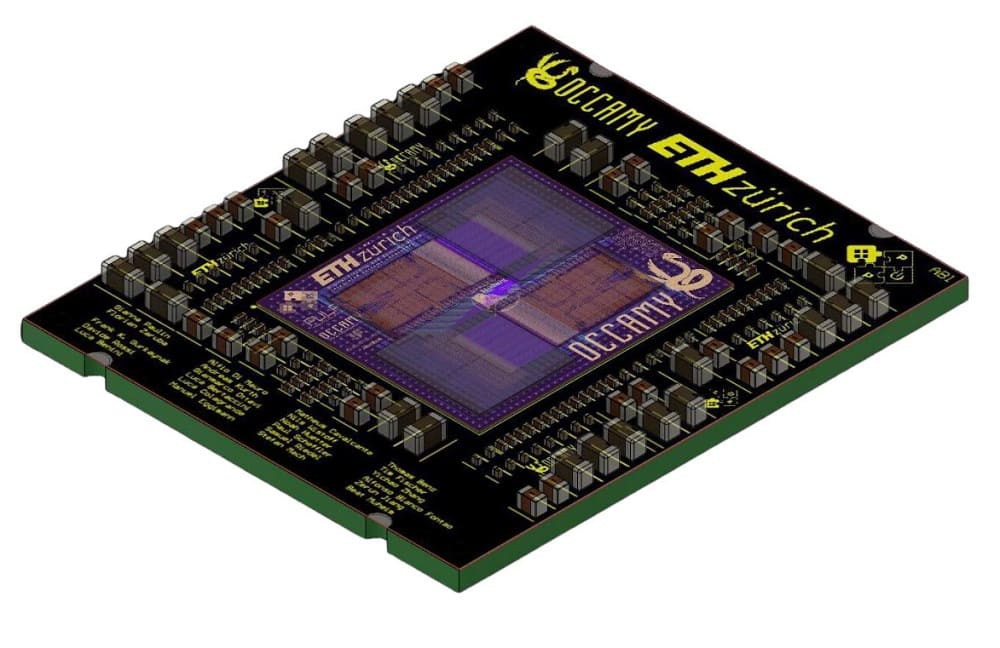

Con unos mil millones de transistores, están empaquetados en una solución de 72 milímetros cuadrados, que se coloca en una PCB portadora de 52,5×45 mm para montaje Fan-Out. Al ser un diseño de chiplet, Occamy utiliza integración 2,5D y cuenta con dos DRAM HBM2E de 16 GB de Micron. Además, el chip dedica un compacto chip de control RISC-V de 32 bits a enrutar la información del resto de núcleos habilitados para IA.

El único die Occamy consume 10 vatios a 1000 MHz de velocidad, por lo que dos dies más la memoria HBM duplicarían con creces el consumo energético del chip final. El chip no solo se ha testeado con AMD Xilinx Virtex UltraScale+ HBM y las FPGA Virtex UltraScale+ VCU1525, sino que también se ha fabricado en menos de 15 meses. Terminado el 1 de julio de 2022, el chip comenzó su desarrollo el 20 de abril de 2021. Se está ensamblando todo el chip y se dispondrá de más información en el tercer trimestre de 2023.

Vía: TechPowerUp