En el VLSI Symposium 2023, que se celebrará entre el 11 y el 16 de junio, Intel demostrará el funcionamiento eficiente de su tecnología PowerVia en un chip E-Core construido con el nodo Intel 4. Los chips convencionales disponen de interconexiones de alimentación y señales distribuidas en varias capas metálicas.

PowerVia, por su parte, dedica capas específicas al suministro energético, separándolas de hecho de las capas de enrutamiento de señales. Este enfoque permite el suministro vertical de energía a través de un conjunto de vías a través del silicio (TSV) o PowerVias, que son esencialmente conexiones verticales entre las superficies superior e inferior del chip.

Al suministrar energía directamente desde la parte posterior del chip, PowerVia reduce el ruido de la fuente de alimentación y las pérdidas resistivas, optimizando la distribución de potencia y mejorando la eficiencia energética global. PowerVia debutará en 2024 con el nodo Intel 20A.

Para la conferencia VLSI Symposium 2023, la compañía ha preparado un documento en el que destaca un diseño realizado con tecnología Intel 4 y que implementa E-Cores únicamente en un chip de prueba.

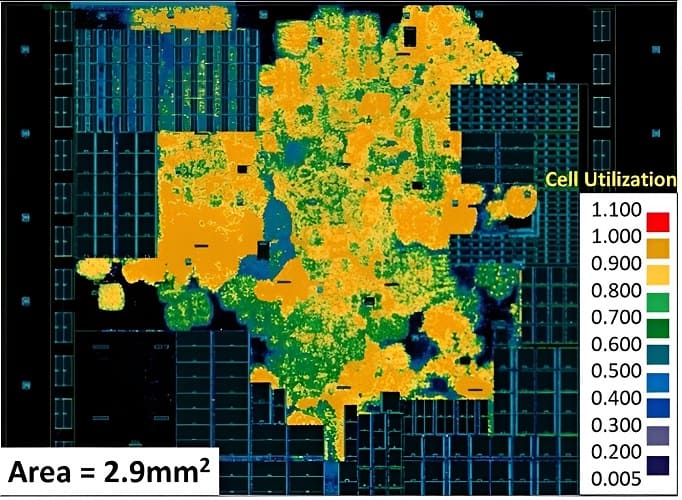

El documento afirma: «La tecnología PowerVia supone una novedosa innovación para ampliar el escalado de procesos mediante el suministro energético en la parte posterior. Este artículo presenta los resultados pre y post silicio de la implementación de un núcleo Intel E-Core con tecnología PowerVia. PowerVia permitió una utilización de celdas estándar superior al 90% en amplias zonas del núcleo, a la vez que mostraba un beneficio de frecuencia superior al 5% en silicio gracias a la reducción de la caída de IR. Se ha demostrado el éxito de la depuración post-silicio con tiempos ligeramente superiores pero aceptables. Las características térmicas del chip de prueba PowerVia están en línea con las mayores densidades de potencia que se esperan del escalado lógico».

PowerVia no sólo proporciona una mejor frecuencia y una menor caída de IR, sino que la gestión térmica también supone una ventaja significativa. A medida que se amplía la lógica, cada vez existen más transistores en menos espacio, lo que incrementa la densidad térmica.

Los PowerVia deberían permitir que eso represente un problema menor y contribuir a que el calor se evacue de forma más eficiente. Aunque PowerVia está previsto para el nodo Intel 20A, la compañía lo implementó en el nodo Intel 4 para aprender y presentar cómo funciona y cómo se implementa a los clientes de Intel Foundry Service (IFS).

Vía: TechPowerUp