Con el objetivo de mejorar el rendimiento y la capacidad de lectura y escritura, los ingenieros de ambas compañías trabajan en el desarrollo de dispositivos 3D NAND de 8 planos y 3D NAND ICs con más de 300 capas.

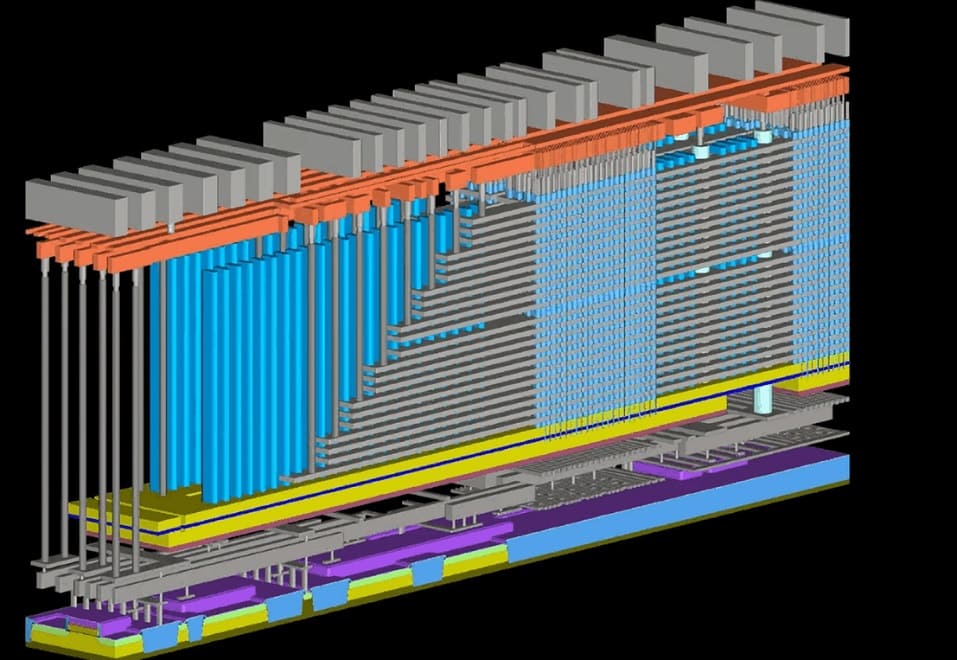

Kioxia, en colaboración con su socio fabricante Western Digital, se prepara para mostrar sus innovaciones de vanguardia en dispositivos de memoria 3D NAND en el Simposio 2023 sobre Tecnología y Circuitos VLSI. Kioxia presentará un documento en el que se describe su dispositivo 3D TLC NAND de 1Tb y ocho planos, con más de 210 capas activas y una interfaz de 3,2 GT/s.

Este innovador dispositivo presenta una latencia de lectura de solo 40 μs y un rendimiento de programa de 205 MB/s. El innovador método de un pulso y dos tiempos de Kioxia y los decodificadores híbridos de direcciones de fila ayudan a resolver la congestión del cableado, lo que reduce el tiempo de detección y acelera la transferencia de datos.

Además, las compañías están avanzando en el desarrollo de dispositivos 3D NAND con más de 300 capas de palabras activas, utilizando técnicas de cristalización lateral inducida por metal («Metal Induced Lateral Crystallization», MILC).

Gracias al empleo del níquel y otras técnicas de vanguardia, este 3D NAND IC ha logrado reducir el ruido de lectura en al menos un 40% y multiplicar por diez la conductancia de los canales sin comprometer la fiabilidad de las celdas.

Tokyo Electron, fabricante de equipos de fabricación de obleas, expondrá su tecnología de grabado dieléctrico de alta relación de aspecto (HAR), que permite fabricar nodos 3D NAND de 400 capas con canales verticales de más de 10 micras en solo 33 minutos, reduciendo al mismo tiempo la huella de carbono en un 84%.

Vía: Guru3D