Hemos recibido una nota de prensa por parte de Intel, os la dejamos a continuación:

Nuevas arquitecturas y tecnologías de Intel creadas para aprovechar las mayores oportunidades del mercado

Intel realiza demostraciones de sistemas para redes, centros de datos y PC basados en tecnología de 10nm, además de la arquitectura de próxima generación ‘Sunny Cove’, tecnología para criptoaceleración y la primera tecnología 3D para microprocesadores del sector

En el Intel Architecture Day el martes 11 de diciembre de 2018, Raja Koduri, arquitecto jefe de Intel, vicepresidente senior de Core and Visual Computing Group y gerente general de Edge Computing Solutions, explica cómo la compañía está posicionada para ofrecer productos de liderazgo en arquitecturas y Cargas de trabajo para un mercado centrado en datos en expansión. (Crédito: Intel Corporation)

En el “Architecture Day” de Intel, los más destacados ejecutivos, arquitectos y socios de la compañía dieron a conocer la próxima generación de tecnologías y se ocuparon del progreso de la estrategia para impulsar el desarrollo de un número cada vez mayor de cargas de trabajo que precisan una enorme cantidad de datos en PC y en otros dispositivos de consumo inteligentes, además de comentar los últimos avances de las redes de alta velocidad, la inteligencia artificial (AI) omnipresente, los centros de datos especializados en la nube y los vehículos autónomos.

Intel realizó demostraciones de una serie de sistemas basados en tecnología de 10 nm que se encuentran en fase de desarrollo para PC, centros de datos y redes, y avanzó las tecnologías diseñadas para una gama cada vez más amplia de cargas de trabajo.

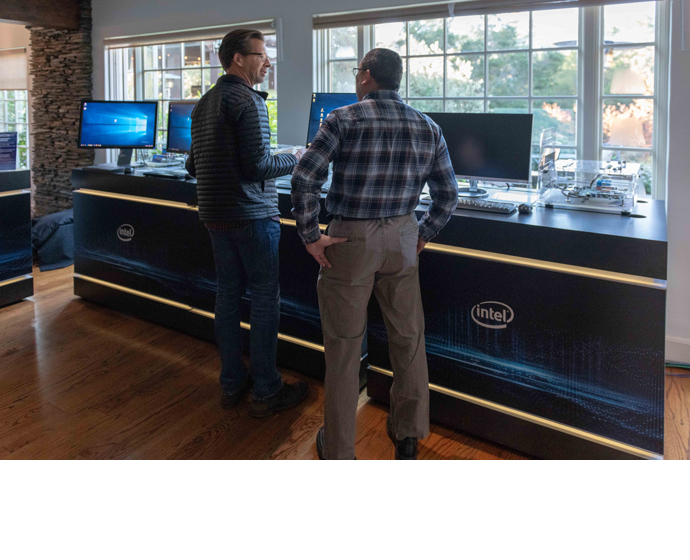

Las personas que asistieron al Intel Architecture Day el martes 11 de diciembre de 2018, experimentan demostraciones que muestran las últimas innovaciones tecnológicas y de arquitectura de Intel. (Crédito: Intel Corporation)

La compañía también dio a conocer su estrategia técnica centrada en seis segmentos de ingeniería, en donde importantes inversiones y una significativa innovación esperan impulsar grandes avances en rendimiento y mejoras en las experiencias de los usuarios, incluyendo novedades en procesamiento y empaquetado de chips, para proporcionar un alto rendimiento y bajo consumo en formatos más reducidos; nuevas arquitecturas para acelerar tareas especializadas como la inteligencia artificial; gráficas y redes; tecnología de memoria ultrarrápida; interconexiones de alto ancho de banda; prestaciones de seguridad embebidas y un software común para facilitar la programación e incrementar el rendimiento.

Juntas, estas tecnologías establecen una base para una era informática más diversa, además de ofrecer una oportunidad de mercado potencial por encima de $300.000 millones en 2022.

Entre los aspectos más destacados de la Arquitectura de Intel podemos destacar:

El primer apilado 3D de microprocesadores en el sector: Intel realizó una demostración de la primera tecnología de empaquetado 3D, llamada “Foveros” que, por primera vez, ofrece los beneficios del apilado 3D para facilitar la integración de chips sobre chips.

Foveros abre el camino para la creación de dispositivos y sistemas que combinan un alto rendimiento con alta densidad y tecnologías de procesamiento basadas en silicio de bajo consumo. Se espera que Foveros amplíe su capacidad de apilado de chips para ir más allá de los intermediadores pasivos tradicionales y de la memoria apilada para llegar a los procesadores de alto rendimiento, como los de CPU, gráficas y, por vez primera, los de IA.

En el Intel Architecture Day, el martes 11 de diciembre de 2018, Murthy Renduchintala, presidente del grupo Intel de Tecnología, Arquitectura de Sistemas & amp; Client Group y director de ingeniería, dirigen una conversación sobre la evolución de la compañía de un proveedor de CPU a un proveedor de plataformas de unidad de procesamiento cruzado (o xPU), demostrando nuevas tecnologías de próxima generación. (Crédito: Intel Corporation)

La tecnología ofrecerá una tremenda flexibilidad a medida que los diseñadores deseen “combinar” los bloques tecnológicos de IP con varios elementos de memoria y E/S en dispositivos de nuevos formatos. Eso permitirá a los productos dividirse en “chiplets” más pequeños, en donde la E/S, el SRAM y los circuitos para suministro de energía se puedan fabricar en un chip base con chiplets de alto rendimiento apilados.

Intel espera lanzar una serie de productos equipados con Foveros a partir de la segunda mitad de 2019. El primer producto con Foveros combinará un chiplet de alto rendimiento basado en una pila informática elaborado con tecnología de 10nm con un chip base 22FFL de bajo consumo, para ofrecer un rendimiento de primera clase y una gran eficiencia energética en un formato pequeño.

En el Intel Architecture Day el martes 11 de diciembre de 2018, Raja Koduri (izquierda), arquitecta jefe de Intel, vicepresidente senior del Core and Visual Computing Group y gerente general de Edge Computing Solutions, y Murthy Renduchintala, presidente del grupo Intel de Tecnología , Arquitectura de Sistemas & amp; El Grupo de clientes y el director de ingeniería explican el rol de Intel en la entrega de productos de liderazgo para un mercado en expansión centrado en los datos. (Crédito: Intel Corporation)

Foveros representa el primer paso hacia adelante después del innovador empaquetado 2D con tecnología EMIB (Embedded Multi-die InterConnect Bridge) de Intel, presentado en 2018.

Nueva arquitectura para CPU Sunny Cove: Intel mostró Sunny Cove, la siguiente generación de la microarquitectura para CPU de Intel, diseñada para incrementar el rendimiento por reloj y la eficiencia energética para tareas informáticas de uso general, además de incluir nuevas prestaciones para acelerar tareas informáticas de uso específico, como las de IA y criptografía. La arquitectura Sunny Cove va a ser la base para la próxima generación de procesadores de Intel para servidores (Intel® Xeon®) y equipos cliente (Intel® Core™) a finales del año que viene. Entre las prestaciones de Sunny Cove se incluye:

- Mejora de microarquitectura para realizar más operaciones en paralelo.

- Nuevos algoritmos para reducir la latencia.

- Aumento del tamaño de los búfer y cachés principales, para optimizar las cargas de trabajo centradas en los datos.

- Ampliaciones de la arquitectura para casos de uso específicas y algoritmos. Por ejemplo, nuevas instrucciones para potenciar el rendimiento en criptografía, como las de Vector AES y SHA-NI, y otros casos de uso críticos como los de compresión/descompresión.

Sunny Cove reduce la latencia e incrementa el rendimiento, además de ofrecer un paralelismo mucho mayor para mejorar las experiencias tanto en juegos como en aplicaciones para medios o las basadas en datos.

Gráficas de próxima generación: Intel dio a conocer la nueva Gen11 de gráficas integradas con 64 unidades de ejecución mejoradas, más del doble que la gráfica Intel Gen9 (24 unidades de ejecución) anterior, superando la barrera de 1 TFLOP. La nueva gráfica integrada se ofrecerá en los procesadores basados en tecnología de 10nm a partir de 2019.La nueva arquitectura de gráficas integradas proporciona el doble de rendimiento informático por reloj en comparación con las gráficas Intel Gen9. Con más de 1 TFLOP de rendimiento, esta arquitectura ha sido diseñada para mejorar en gran medida la experiencia a la hora de participar en juegos. Las gráficas de Gen11 pueden casi duplicar el rendimiento de la tecnología para IA en algunas de las aplicaciones para inferencia de consuno más populares, como, por ejemplo, el reconocimiento de imágenes. Las gráficas de Gen11 también contarán con los codificadores y descodificadores de medios más avanzados del sector, con soporte a transmisiones de vídeo 4K y creación de contenidos 8K en entornos de consumo limitado. La tecnología Gen11 también cuenta con la tecnología Adaptive Sync que permite una rápida velocidad de imagen para juegos.Intel también reafirmó sus planes para presentar su primer procesador para gráficas discretas en 2020.

Software “One API”: Intel anunció el proyecto “One API” para simplificar la programación de diversos motores informáticos en CPU, GPU, FPGA, AI y otros aceleradores. El proyecto incluye una cartera de herramientas para desarrolladores completas y unificadas para la asignación de software a hardware y así acelerar mejor el código. Se espera que una versión pública del proyecto se encuentre disponible en 2019.

Memoria y almacenamiento: Intel comunicó nuevas noticias sobre las tecnologías y los productos basados en tecnología Intel® Optane™. La memoria persistente Intel® Optane™ DC es un nuevo producto que integra la memoria más próxima al CPU para acelerar el procesamiento de unos conjuntos de datos más amplios, como los que se utilizan en IA. La memoria persistente Intel Optane DC ofrece al CPU 64B de línea de cache para lectura. Como media, esperamos que la latencia media de lectura en inactividad del subsistema con memoria persistente Optane se encuentre en, aproximadamente, 350 nanosegundos cuando los datos solicitados no se encuentren en la DRAM, o cuando la aplicación dirija la operación a la memoria persistente Optane. Un SSD Optane DC tiene una latencia media de lectura en inactividad de, aproximadamente, 10.000 nanosegundos (10 microsegundos), lo que representa una mejora considerable.

La compañía también dio a conocer la capacidad de los SSD basados en chip Intel NAND QLC de 1 Terabit para llevar grandes cantidades de datos desde un HDD a un SSD, permitiendo al mismo tiempo un acceso rápido a esos datos.

La combinación del SSD Intel Optane y del SSD QLC NAND permitirá un acceso con menor latencia a los datos que se usan con mayor frecuencia. Conjuntamente, estos avances en plataformas y memorias servirán de complemento a la cartera de soluciones y proporcionarán el conjunto más apropiado de productos para sistemas y aplicaciones disponibles en el mercado.

- Deep Learning Reference Stack: Intel ha informado sobre el Deep Learning Reference Stack, una pila de código abierto integrada y de alto rendimiento para plataformas basadas en procesadores escalables Intel® Xeon®. Esta versión para la comunidad de código abierto forma parte de nuestros esfuerzos para garantizar a los desarrolladores de IA el fácil acceso a todas las prestaciones y funciones de las plataformas Intel. El Deep Learning Reference Stack ha sido creado y optimizado para entornos nativos en la nube. Con esta versión, facilitamos a los desarrolladores la elaboración rápida de prototipos, reduciendo al mismo tiempo la complejidad asociada con la integración de múltiples componentes de software, ofreciendo a los usuarios la flexibilidad que necesitan para personalizar sus soluciones.

- Sistema operativo: Clear Linux* OS personalizable para las necesidades de cada desarrollador, optimizado para las plataformas Intel y para casos de uso específicos como el aprendizaje profundo.

- Orquestación: los kubernetes gestionan y orquestan aplicaciones contenerizadas para un clúster multimodo con conocimiento de plataformas Intel.

- Contenedores: Docker Containers y Kata Containers que utilizan tecnología Intel VT para asegurar los contenedores.

- Bibliotecas: Intel® Math Kernel Library for Deep Neural Networks (MKL DNN) es la biblioteca matemática altamente optimizada de Intel para rendimiento de funciones matemáticas.

- Tiempos de ejecución: Python ofrece soporte al tiempo de ejecución de aplicaciones y servicios y se encuentra altamente optimizado para la arquitectura de Intel.

- Marcos: TensorFlow es un marco líder para aprendizaje profundo y aprendizaje automático.

- Instalación: KubeFlow es una herramienta de instalación impulsada por el sector de código abierto que ofrece una rápida experiencia en IA, además de facilitar la instalación y ser sencillo de usar cuando se encuentra instalado.

- En el Día de la Arquitectura de Intel, el martes 11 de diciembre de 2018, Jim Keller, vicepresidente senior y gerente general de Intelon Silicon Engineer Group, explica cómo la compañía está posicionada para ofrecer productos de liderazgo en arquitecturas y cargas de trabajo para una expansión centrada en los datos. mercado. (Crédito: Intel Corporation)